良好電源設(shè)計(jì)有利于提升鎖相環(huán)性能

摘要:鎖相環(huán)是現(xiàn)代通信系統(tǒng)的基本構(gòu)建模塊,而電源噪聲越來越影響鎖相環(huán)性能。本文通過列舉多種電源管理電路設(shè)計(jì)的新方法,解析不同的設(shè)計(jì)對(duì)鎖相環(huán)性能產(chǎn)生的影響。

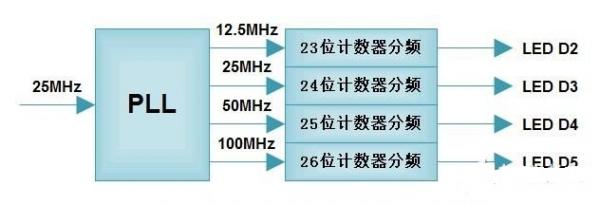

本文引用地址:http://www.104case.com/article/136874.htm鎖相環(huán)(PLL)是現(xiàn)代通信系統(tǒng)的基本構(gòu)建模塊。PLL通常用于在無線電設(shè)備中提供本振(LO)功能,也可用于時(shí)鐘信號(hào)分配和降噪,而且還用作高采樣速率模數(shù)或數(shù)模轉(zhuǎn)換的時(shí)鐘源。

由于每一代PLL的噪聲性能都在改善,因此電源噪聲的影響變得越來越明顯,某些情況下甚至可限制噪聲性能。

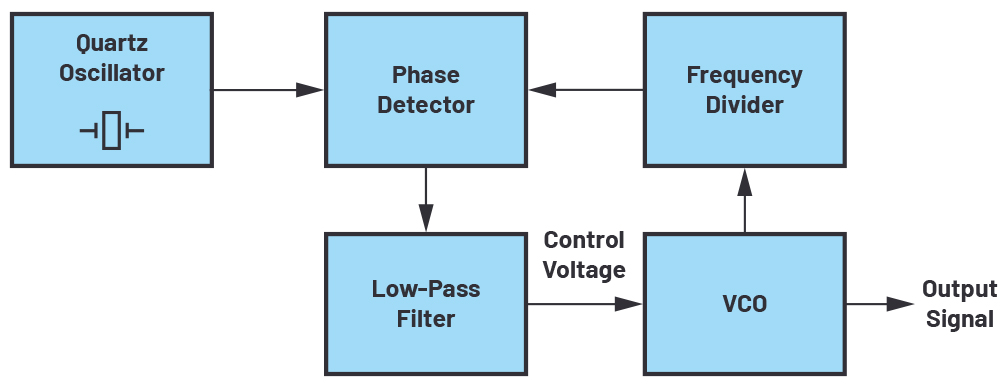

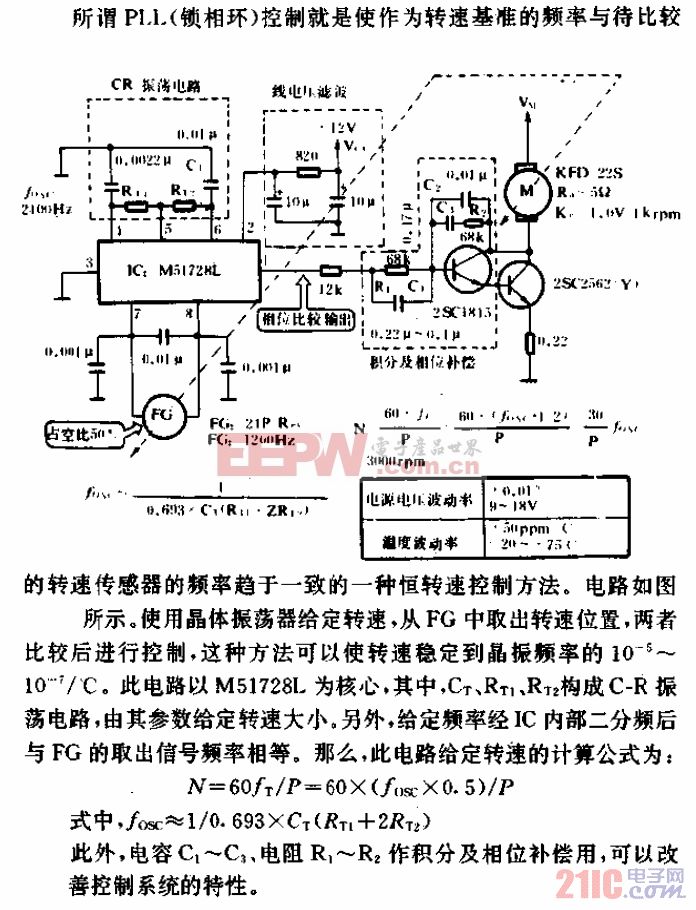

PLL中,反饋控制環(huán)路驅(qū)動(dòng)電壓控制振蕩器(VCO),使壓控振蕩器頻率(或相位)精確跟蹤所施加參考頻率的倍數(shù)頻率。VCO將來自鑒相器的誤差電壓轉(zhuǎn)換成輸出頻率。它的“增益”(KVCO)通常以MHz/V表示。

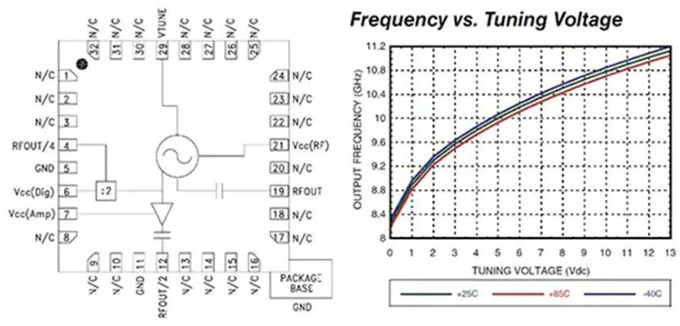

電壓控制可變電容二極管(變?nèi)荻O管)常用于調(diào)節(jié)VCO內(nèi)的頻率。KVCO通常比較大,以提供足夠的頻率覆蓋范圍,但又不能太大而影響相位噪聲,因?yàn)槿魏巫內(nèi)荻O管噪聲都會(huì)被放大KVCO倍,進(jìn)而增加輸出相位噪聲。

多頻段集成VCO的出現(xiàn)可避免在KVCO與頻率覆蓋范圍間進(jìn)行取舍,使PLL設(shè)計(jì)人員可以使用具有智能頻段切換程序的包含數(shù)個(gè)適度增益VCO的IC,為編程輸出頻率選擇適當(dāng)?shù)念l段。這種解決方案可提供寬廣的總體范圍和較低的噪聲。

電源波動(dòng)可能導(dǎo)致額外的意外輸出頻率變化。VCO對(duì)電源波動(dòng)的靈敏度定義為VCO推壓(Kpushing)。較高的VCO推壓意味著VCO對(duì)電源噪聲的增加倍數(shù)更大,因此,為了盡可能降低對(duì)VCO相位噪聲的影響,需要低噪聲電源。

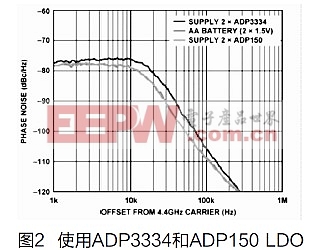

不同的低壓差調(diào)節(jié)器(LDO)可能影響PLL相位噪聲。例如,對(duì)ADP3334和ADP150 LDO為ADF4350供電時(shí)的性能進(jìn)行比較的結(jié)果顯示,ADP3334調(diào)節(jié)器的積分rms噪聲為27μV(4個(gè)十倍頻程,從10 Hz至100 kHz)。該結(jié)果可與ADP150的9μV比較。

圖2中可以看出已測(cè)量PLL相位噪聲頻譜密度的差異。這是最差情況結(jié)果(在VCO推壓最大值頻率測(cè)量)。ADP150調(diào)節(jié)器噪聲足夠低,不會(huì)降低VCO噪聲性能,使用兩節(jié)AA電池重復(fù)測(cè)量可確認(rèn)這一點(diǎn)。

評(píng)論