在進行FPGA設(shè)計時,有很多需要我們注意的地方。具有好的設(shè)計風(fēng)格才能做出好的設(shè)計產(chǎn)品,這一點是毋庸置疑的。那么,接下來,小編就帶大家一起來看看,再進行FPGA設(shè)計時,我們都要注意哪些呢? 一.命名風(fēng)格: 1不

關(guān)鍵字:

FPGA 電子工程師 經(jīng)驗

隨著高速數(shù)字系統(tǒng)的發(fā)展,高速串行數(shù)據(jù)被廣泛使用,內(nèi)嵌高速串行接口的FPGA也得到大量應(yīng)用,相應(yīng)的高速串行信號質(zhì)量的測試也越來越頻繁和重要。通常用示波器觀察信號波形、眼圖、抖動來衡量信號的質(zhì)量,Xilinx提供的

關(guān)鍵字:

FPGA 集成式 比特 誤碼率測試儀

1 引言隨著社會的發(fā)展。使用電梯越來越普遍,已從原來只在商業(yè)大廈、賓館過渡到在辦公室、居民樓等多種建筑中,并且對電梯功能的要求也不斷提高,其相應(yīng)控制方式也在不斷發(fā)生變化。電梯的微機化控制主要有:PLC控制、

關(guān)鍵字:

CPLD VDHL 器件 電梯控制系統(tǒng)

摘要:通過分析各種偽隨機序列生成方法,提出了一種基于M 序列的連續(xù)抽樣方法,可以生 成滿足自適應(yīng)光學(xué)系統(tǒng)SPGD 控制算法要求的多路、相互獨立以及服從伯努利分布的偽隨機序 列。該方法適合于用FPGA 等超大規(guī)模集成

關(guān)鍵字:

FPGA 偽隨機序列 方法

摘要:本設(shè)計基于DDS原理和FPGA技術(shù)按照順序存儲方式,將對正弦波、方波、三角波、鋸齒波四種波形的取樣數(shù)據(jù)依次全部存儲在ROM波形表里,通過外接設(shè)備撥扭開關(guān)和鍵盤控制所需波形信號的輸出,最終將波形信息顯示在LC

關(guān)鍵字:

FPGA DDS 信號發(fā)生器

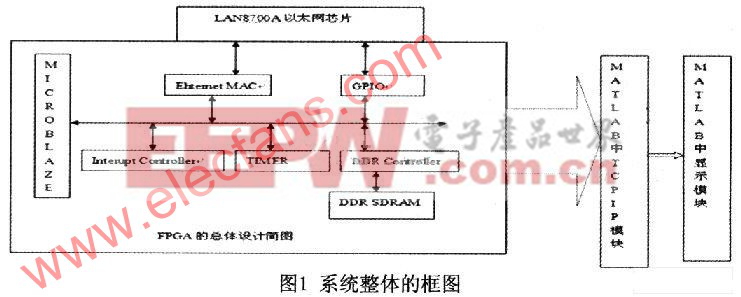

O 引言 近年來,隨著信息技術(shù)的發(fā)展,網(wǎng)絡(luò)化日加普遍,以太網(wǎng)被廣泛應(yīng)用到各個領(lǐng)域。例如在數(shù)據(jù)采集領(lǐng)域,一些小型監(jiān)測設(shè)備需要增加網(wǎng)絡(luò)實現(xiàn)遠(yuǎn)程數(shù)據(jù)傳輸?shù)墓δ埽灰切┰O(shè)備上增加一個網(wǎng)絡(luò)接口并實現(xiàn)了TCP/IP協(xié)

關(guān)鍵字:

通信 Matlab 系統(tǒng) 研究 協(xié)議 基于 TCP IP FPGA

過去,TMOEM設(shè)計的儀器都是根據(jù)某種標(biāo)準(zhǔn)完成測試過程。這樣,當(dāng)一個新的標(biāo)準(zhǔn)或修訂后的標(biāo)準(zhǔn)發(fā)布出來時,他...

關(guān)鍵字:

便攜式 測試設(shè)備 FPGA

FPGA在廣播視頻中的應(yīng)用, 1.時機

關(guān)鍵字:

應(yīng)用 視頻 廣播 FPGA

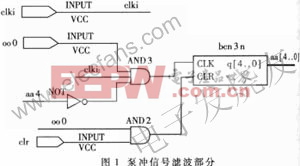

基于CPLD的數(shù)字濾波及抗干擾實現(xiàn),1 濾波和抗干擾概述

關(guān)鍵字:

抗干擾 實現(xiàn) 波及 數(shù)字 CPLD 基于

1 引 言在ARM+FPGA系統(tǒng)結(jié)構(gòu)中,實現(xiàn)基于ARM的嵌入式處理器和FPGA之間通信最簡單的方法就是通過異步串行接口EIARS232C。考慮選用集成有UART(Universal Asynchronous Receiver / TraNSmitter )控制器的嵌入式處理器

關(guān)鍵字:

UART FPGA

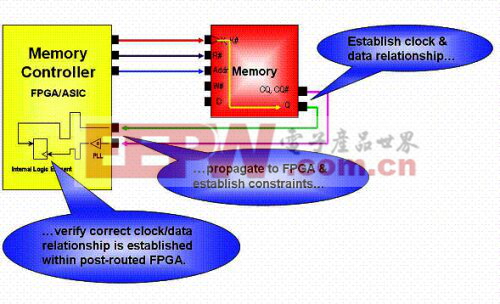

如何有效的管理FPGA設(shè)計中的時序問題, 當(dāng)

關(guān)鍵字:

時序 問題 設(shè)計 FPGA 有效 管理 如何

摘要:為了消除空間環(huán)境中單粒子翻轉(zhuǎn)(SEU)的影響,目前星載計算機中均對RAM存儲單元采用檢錯糾錯(EDAC)設(shè)計。隨著FPGA在航天領(lǐng)域的廣泛應(yīng)用,FPGA已成為EDAC功能實現(xiàn)的最佳硬件手段。本文介紹了EDAC的編碼和實現(xiàn),提出一

關(guān)鍵字:

FPGA EDAC 星載 計算機

摘要:現(xiàn)在嵌入式系統(tǒng)的功能越來越集合化,需要控制大量外設(shè)。外設(shè)模塊普遍采用UART作為通信接口,但是通常處理器都會自帶一個UART串口。實際應(yīng)用中一個串口往往不夠用,需要對系統(tǒng)進行擴展。本文所介紹的就是以FPGA為實

關(guān)鍵字:

FPGA UART 總線設(shè)計

摘要:為了提高水聲傳感器網(wǎng)絡(luò)通信系統(tǒng)試驗和算法研究的效率,水聲傳感器網(wǎng)絡(luò)節(jié)點需要具有水聲通信的原始波形數(shù)據(jù)的記錄功能。本文設(shè)計了一種水聲信號采樣存儲系統(tǒng),實現(xiàn)了數(shù)據(jù)變速率AD采集、數(shù)據(jù)環(huán)形存儲、數(shù)據(jù)連續(xù)

關(guān)鍵字:

FPGA 水聲信號 采樣 存儲

摘要:在時差定位(TDOA)技術(shù)中,高精度的時差測量是準(zhǔn)確定位的關(guān)鍵。針對這一需要, 提出一種基于FPGA 的高精度時差測量系統(tǒng)的實現(xiàn)方案。本系統(tǒng)的時差測算單元以Altera 公司Cyclone 系列的EP1C3T144 芯片為核心,并提

關(guān)鍵字:

FPGA 高精度 時差測量 系統(tǒng)設(shè)計

cpld/fpga介紹

您好,目前還沒有人創(chuàng)建詞條cpld/fpga!

歡迎您創(chuàng)建該詞條,闡述對cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。

創(chuàng)建詞條

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473