active-hdl 文章 最新資訊

實(shí)驗(yàn)17:分頻器

- 實(shí)驗(yàn)?zāi)康模?)熟悉和掌握FPGA開發(fā)流程和Lattice Diamond軟件使用方法;(2)通過實(shí)驗(yàn)理解和掌握分頻器原理;(3)學(xué)習(xí)用Verilog HDL行為級(jí)描述時(shí)序邏輯電路。實(shí)驗(yàn)任務(wù)設(shè)計(jì)一個(gè)任意整數(shù)分頻器。實(shí)驗(yàn)原理時(shí)鐘信號(hào)的處理是FPGA的特色之一,因此分頻器也是FPGA設(shè)計(jì)中使用頻率非常高的基本設(shè)計(jì)之一。一般在FPGA中都有集成的鎖相環(huán)可以實(shí)現(xiàn)各種時(shí)鐘的分頻和倍頻設(shè)計(jì),但是通過語言設(shè)計(jì)進(jìn)行時(shí)鐘分頻是最基本的訓(xùn)練,在對(duì)時(shí)鐘要求不高的設(shè)計(jì)時(shí)也能節(jié)省鎖相環(huán)資源。在本實(shí)驗(yàn)中我們將實(shí)現(xiàn)任意整數(shù)的分頻器,分頻

- 關(guān)鍵字: 分頻器 FPGA Lattice Diamond Verilog HDL

實(shí)驗(yàn)16:扭環(huán)形計(jì)數(shù)器

- 實(shí)驗(yàn)?zāi)康模?)熟悉和掌握FPGA開發(fā)流程和Lattice Diamond軟件使用方法;(2)通過實(shí)驗(yàn)理解和掌握扭環(huán)形計(jì)數(shù)器原理;(3)學(xué)習(xí)用Verilog HDL行為級(jí)描述時(shí)序邏輯電路。實(shí)驗(yàn)任務(wù)設(shè)計(jì)一個(gè)右移扭環(huán)形計(jì)數(shù)器。實(shí)驗(yàn)原理將移位寄存器的輸出非q0連接到觸發(fā)器q3的輸入,這樣就構(gòu)成了一個(gè)扭環(huán)形計(jì)數(shù)器。初始化復(fù)位時(shí),給q0一個(gè)初值0000,則在循環(huán)過程中依次為:000010001100111011110111001100010000。Verilog HDL建模描述用行為級(jí)描述右移扭環(huán)形計(jì)數(shù)器程序清單tw

- 關(guān)鍵字: 扭環(huán)形計(jì)數(shù)器 FPGA Lattice Diamond Verilog HDL

實(shí)驗(yàn)15:環(huán)形計(jì)數(shù)器

- 實(shí)驗(yàn)?zāi)康模?)熟悉和掌握FPGA開發(fā)流程和Lattice Diamond軟件使用方法;(2)通過實(shí)驗(yàn)理解和掌握環(huán)形計(jì)數(shù)器原理;(3)學(xué)習(xí)用Verilog HDL行為級(jí)描述時(shí)序邏輯電路。實(shí)驗(yàn)任務(wù)設(shè)計(jì)一個(gè)4位右循環(huán)一個(gè)1的環(huán)形計(jì)數(shù)器。實(shí)驗(yàn)原理將移位寄存器的輸出q0連接到觸發(fā)器q3的輸入,并且在這4個(gè)觸發(fā)器中只有一個(gè)輸出為1,另外3個(gè)為0,這樣就構(gòu)成了一個(gè)環(huán)形計(jì)數(shù)器。初始化復(fù)位時(shí),給q0一個(gè)置位信號(hào),則唯一的1將在環(huán)形計(jì)數(shù)器中循環(huán)移位,每4個(gè)時(shí)鐘同期輸出一個(gè)高電平脈沖。Verilog HDL建模描述用行為級(jí)描述

- 關(guān)鍵字: 環(huán)形計(jì)數(shù)器 FPGA Lattice Diamond Verilog HDL

實(shí)驗(yàn)14:移位寄存器

- 實(shí)驗(yàn)?zāi)康模?)熟悉和掌握FPGA開發(fā)流程和Lattice Diamond軟件使用方法;(2)通過實(shí)驗(yàn)理解和掌握移位寄存器原理;(3)學(xué)習(xí)用Verilog HDL行為級(jí)描述時(shí)序邏輯電路。實(shí)驗(yàn)任務(wù)本實(shí)驗(yàn)的任務(wù)是設(shè)計(jì)一個(gè)7位右移并行輸入、串行輸出的移位寄存器。實(shí)驗(yàn)原理如果將多個(gè)觸發(fā)器級(jí)聯(lián)就構(gòu)成一個(gè)多位的移位寄存器,如下圖所示,是以4位移位寄存器為例的邏輯電路圖,其中的LD/SHIFT是一個(gè)置數(shù)/移位控制信號(hào)。當(dāng)LD/SHIFT為1時(shí),在CP作用下,從輸入端A、B、C、D并行接收數(shù)據(jù);當(dāng)LD/SHIFT為0時(shí),在

- 關(guān)鍵字: 移位寄存器 FPGA Lattice Diamond Verilog HDL

實(shí)驗(yàn)13:JK觸發(fā)器

- 實(shí)驗(yàn)?zāi)康模?)熟悉和掌握FPGA開發(fā)流程和Lattice Diamond軟件使用方法;(2)通過實(shí)驗(yàn)理解和掌握J(rèn)K觸發(fā)器原理;(3)學(xué)習(xí)用Verilog HDL語言行為機(jī)描述方法描述JK觸發(fā)器電路。實(shí)驗(yàn)任務(wù)本實(shí)驗(yàn)的任務(wù)是設(shè)計(jì)一個(gè)JK觸發(fā)器實(shí)驗(yàn)原理帶使能端RS鎖存器的輸入端R=S=1時(shí),鎖存器的次態(tài)不確定,這一因素限制了其應(yīng)用。為了解決這個(gè)問題,根據(jù)雙穩(wěn)態(tài)元件兩個(gè)輸出端互補(bǔ)的特點(diǎn),用Q和非Q反饋控制輸入信號(hào),并用J代替S,用K代替R,構(gòu)成了J-K鎖存器。Verilog HDL建模描述用行為級(jí)描述實(shí)現(xiàn)的帶異步

- 關(guān)鍵字: JK觸發(fā)器 FPGA Lattice Diamond Verilog HDL

實(shí)驗(yàn)12:邊沿觸發(fā)的D觸發(fā)器

- 實(shí)驗(yàn)?zāi)康模?)熟悉和掌握FPGA開發(fā)流程和Lattice Diamond軟件使用方法;(2)通過實(shí)驗(yàn)理解和掌握D觸發(fā)器原理;(3)學(xué)習(xí)用Verilog HDL語言行為機(jī)描述方法描述D觸發(fā)器電路。實(shí)驗(yàn)任務(wù)本實(shí)驗(yàn)的任務(wù)是描述一個(gè)帶有邊沿觸發(fā)的同步D觸發(fā)器電路,并通過STEP FPGA開發(fā)板的12MHz晶振作為觸發(fā)器時(shí)鐘信號(hào)clk,撥碼開關(guān)的狀態(tài)作為觸發(fā)器輸入信號(hào)d,觸發(fā)器的輸出信號(hào)q和~q,用來分別驅(qū)動(dòng)開發(fā)板上的LED,在clk上升沿的驅(qū)動(dòng)下,當(dāng)撥碼開關(guān)狀態(tài)變化時(shí)LED狀態(tài)發(fā)生相應(yīng)變化。實(shí)驗(yàn)原理從D觸發(fā)器的特

- 關(guān)鍵字: D觸發(fā)器 FPGA Lattice Diamond Verilog HDL

實(shí)驗(yàn)11:RS觸發(fā)器

- 實(shí)驗(yàn)?zāi)康模?)熟悉和掌握FPGA開發(fā)流程和Lattice Diamond軟件使用方法;(2)通過實(shí)驗(yàn)理解和掌握RS觸發(fā)器原理;(3)學(xué)習(xí)用Verilog HDL語言行為級(jí)描述方法描述RS觸發(fā)器電路。實(shí)驗(yàn)任務(wù)本實(shí)驗(yàn)的任務(wù)是描述一個(gè)RS觸發(fā)器電路,并通過STEP FPGA開發(fā)板的12MHz晶振作為觸發(fā)器時(shí)鐘信號(hào)clk,撥碼開關(guān)的狀態(tài)作為觸發(fā)器輸入信號(hào)S,R,觸發(fā)器的輸出信號(hào)Q和非Q,用來分別驅(qū)動(dòng)開發(fā)板上的LED,在clk上升沿的驅(qū)動(dòng)下,當(dāng)撥碼開關(guān)狀態(tài)變化時(shí)LED狀態(tài)發(fā)生相應(yīng)變化。實(shí)驗(yàn)原理基本RS觸發(fā)器可以由兩

- 關(guān)鍵字: RS觸發(fā)器 FPGA Lattice Diamond Verilog HDL

實(shí)驗(yàn)10:七段數(shù)碼管

- 1. 實(shí)驗(yàn)?zāi)康模?)熟悉和掌握FPGA開發(fā)流程和Lattice Diamond軟件使用方法;(2)通過實(shí)驗(yàn)理解和掌握數(shù)碼管驅(qū)動(dòng);(3)學(xué)習(xí)用Verilog HDL描述數(shù)碼管驅(qū)動(dòng)電路。2. 實(shí)驗(yàn)任務(wù)在數(shù)碼管上顯示數(shù)字。3. 實(shí)驗(yàn)原理數(shù)碼管是工程設(shè)計(jì)中使用很廣的一種顯示輸出器件。一個(gè)7段數(shù)碼管(如果包括右下的小點(diǎn)可以認(rèn)為是8段)分別由a、b、c、d、e、f、g位段和表示小數(shù)點(diǎn)的dp位段組成。實(shí)際是由8個(gè)LED燈組成的,控制每個(gè)LED的點(diǎn)亮或熄滅實(shí)現(xiàn)數(shù)字顯示。通常數(shù)碼管分為共陽極數(shù)碼管和共陰極數(shù)碼管,結(jié)構(gòu)如下圖

- 關(guān)鍵字: 七段數(shù)碼管 FPGA Lattice Diamond Verilog HDL

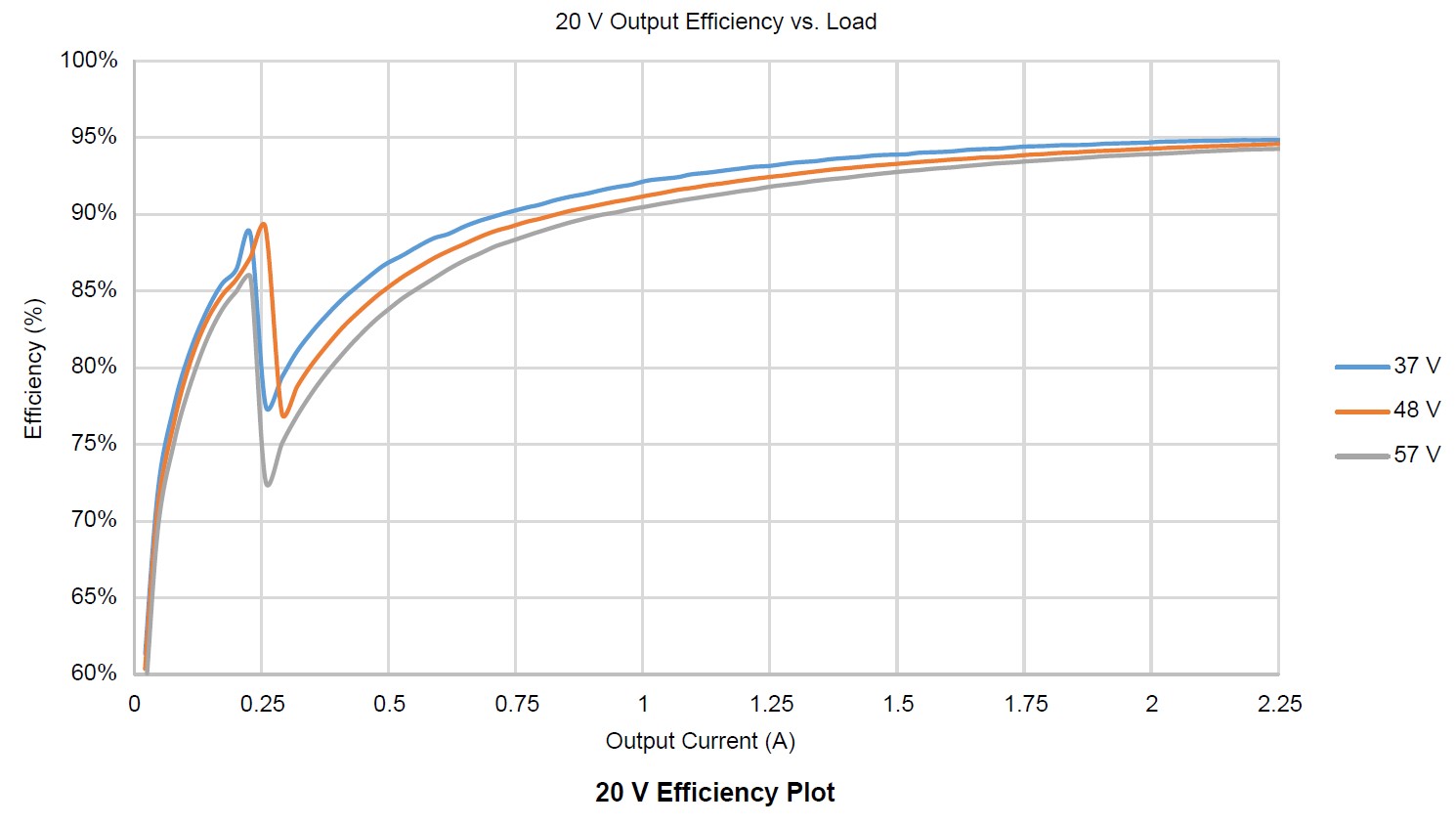

安森美半導(dǎo)體NCP1568D Active Clamp IC+NCP51530+NCP4308+FUSB3307應(yīng)用于45W PoE to USB PD 電源

- 本方案介紹了用于乙太網(wǎng)供電到USB-PD應(yīng)用的45 W通用輸入5 V,9 V,15 V和20 V輸出評(píng)估板,特色是使用安森美半導(dǎo)體的NCP1568D PWM控制器的主動(dòng)箝位返馳式拓?fù)洌钆銷CP51530半橋驅(qū)動(dòng)器及NCP4308同步整流控制器與FUSB3307 USB-PD控制器,實(shí)現(xiàn)經(jīng)由PoE兼容的DC/DC輸入電壓(37V–57V)搭配NCP1568D與FUSB3307元件輸出標(biāo)準(zhǔn)的USB-PD輸出規(guī)格,可應(yīng)用在廣泛的USB-PD裝置的充電需求上。該方案將NCP1568和NCP51530用于主動(dòng)箝位

- 關(guān)鍵字: 安森美 NCP1568D Active Clamp NCP51530 NCP4308 FUSB3307 PoE PD USB

傳三星Galaxy Watch Active 2將搭載可觸控表圈

- 這段時(shí)間有爆料稱三星將會(huì)在8月7日的Galaxy新品發(fā)布會(huì)上同時(shí)推出新一代Galaxy Watch Active設(shè)備。近日,外媒最新消息顯示三星將會(huì)為Galaxy Watch Active 2代配備一個(gè)可觸控的表圈。三星 Galaxy Watch2產(chǎn)品綜述|圖片(1)|參數(shù)|報(bào)價(jià)|點(diǎn)評(píng)網(wǎng)曝三星Galaxy Watch?Active 2將支持表圈觸控?fù)?jù)外媒報(bào)道,用戶通過這種可觸控的表圈可以便捷的對(duì)設(shè)備的進(jìn)行放大、縮小,控制音量,上下瀏覽頁面以及點(diǎn)擊確認(rèn)等操作,可以補(bǔ)足一些因設(shè)備屏幕尺寸過小而造成的

- 關(guān)鍵字: 三星 Galaxy Watch Active 2

Qorvo? 即將收購 Active-Semi International

- 此次收購將會(huì)增加面向互補(bǔ)性高增長應(yīng)用的高度差異化模擬/混合信號(hào)功率解決方案 為 5G、工業(yè)、數(shù)據(jù)中心、汽車和智能家居業(yè)務(wù)增長創(chuàng)造新機(jī)會(huì) 使 QORVO 的潛在市場規(guī)模擴(kuò)大 30 億美元以上 預(yù)計(jì)在收購后第一年實(shí)現(xiàn)根據(jù)非公認(rèn)會(huì)計(jì)準(zhǔn)則計(jì)算的毛利率和每股盈利增加

- 關(guān)鍵字: Qorvo 收購 Active-Semi International Inc

運(yùn)算放大器的有限增益帶寬積對(duì)active-RC濾波器Q值的影響及其補(bǔ)償方法

- 摘要:文章從數(shù)學(xué)上分析了運(yùn)算放大器的有限增益帶寬積對(duì)active-RC濾波器Q值的影響,得出了濾波器Q值升高的結(jié)論,并且研究了濾波器Q值升高的補(bǔ)償方法。

- 關(guān)鍵字: active-RC 運(yùn)算放大器 Q值 濾波器

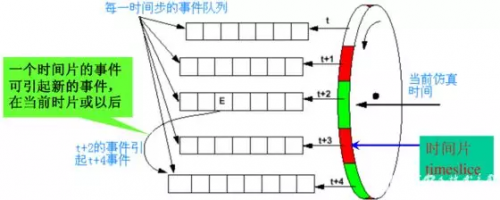

HDL仿真器基于事件的仿真算法

- 目前,HDL仿真器主要有三種實(shí)現(xiàn)算法(機(jī)制):基于時(shí)間的算法(Time-Based)、基于事件的算法(Event-Based,EBS)和基于周期的算法(Cycle-Based,CBS) 基于時(shí)間的算法適合處理連續(xù)的時(shí)間及變量,其會(huì)在每一個(gè)時(shí)間點(diǎn)對(duì)所有的電路元件進(jìn)行計(jì)算。但是,在大部分情況下,每一個(gè)時(shí)間點(diǎn)只有約2%~10%的電路處于活動(dòng)(運(yùn)行)狀態(tài),所以該算法效率非常低。 基于事件的算法適合處理離散的時(shí)間、狀態(tài)和變量。該算法只有在電路狀態(tài)發(fā)生變化時(shí)才進(jìn)行處理,只仿真那些可能引起電路狀態(tài)改變的元件。仿

- 關(guān)鍵字: HDL 仿真器

哈夫曼編碼的HDL實(shí)現(xiàn)

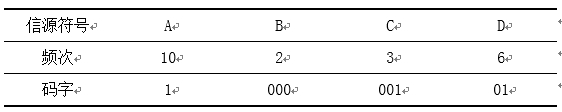

- Huffman編碼是一種可變字長的無損壓縮編碼。根據(jù)字符出現(xiàn)的概率得到的可變字長編碼表是Huffman編碼的核心。概率低的字符使用較短的編碼,概率高的字符使用的長的編碼。 Huffman編碼的具體方法是將序列中的信源符號(hào)先按出現(xiàn)的頻次排序,把兩個(gè)最小的頻次相加,作為新的頻次和剩余的頻次重新排序,再把最小的兩個(gè)頻次相加,再重新排序,直到最后變成序列的總長度。每次挑出的最小兩個(gè)頻次所對(duì)應(yīng)的信源符號(hào)或信源符號(hào)集構(gòu)成二叉樹的左右兩支,對(duì)這左右兩支賦予“0”和“1”的權(quán)重。符號(hào)的編碼從樹的根部開始一直到達(dá)符號(hào)

- 關(guān)鍵字: 哈夫曼編碼 HDL

active-hdl介紹

您好,目前還沒有人創(chuàng)建詞條active-hdl!

歡迎您創(chuàng)建該詞條,闡述對(duì)active-hdl的理解,并與今后在此搜索active-hdl的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)active-hdl的理解,并與今后在此搜索active-hdl的朋友們分享。 創(chuàng)建詞條

熱門主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司