Synopsys推出Synphony高層次綜合

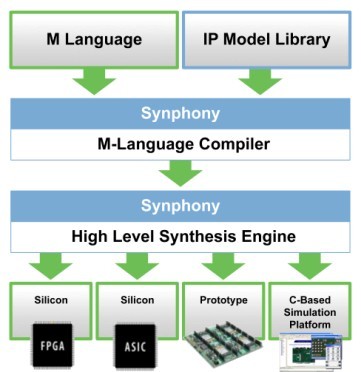

全球領先的半導體設計、驗證和制造軟件、硬件及知識產權(IP)供應商新思科技公司(NASDAQ: SNPS),今天宣布推出其Synphony HLS (High Level Synthesis)解決方案。該解決方案集成了M語言和基于模型的綜合法,與 傳統RTL流程相比,能夠為通信和多媒體應用提供高達10倍速的更高的設計和驗證能力。Synphony HLS為ASIC 和 FPGA的應用、架構和快速原型生成最優化的RTL。此外,通過在虛擬平臺中為系統驗證和早期軟件開發生成C模型,Synphony HLS補充了基于C/C++的程序流。Synphony HLS與Synopsys的綜合工具DC、Synplify Premier、Confirma、VCS、System Studio和Innovator產品一起,提供了從算法到最終芯片的最完整的原型、實施和驗證流程。

本文引用地址:http://www.104case.com/article/98924.htm

Synphony HLS解決方案通過以下優點提供了比傳統方式明顯更高的效率:

- 從M語言到優化RTL的自動流程

- 針對ASIC和FPGA的架構優化生成RTL代碼

- 用于早期算法驗證的快速原型方法

- 生成C模型用于早期軟件開發和快速系統驗證

- 包括原型和ASIC應用在內的多個流程的統一驗證

“Synphony HLS解決方案將顯著地改變FPGA和ASIC在系統驗證和嵌入式軟件開發中的應用方式。” Toyon研究公司的算法開發師Richard Cagley博士說:“傳統的HLS方法繼續承擔著重要的硬件工程資源,將我的算法翻譯成RTL,在FPGA和ASIC芯片上進行運行。Synphony HLS使我能夠用MATLAB®進行高層級仿真和產品編碼,這意味著我現在僅用幾小時或幾天的時間就能夠直接從仿真到達硬件,而不用數月或數年的時間。這對基于我們算法的生產力、生產進度和產品質量有廣泛的影響。”

從M語言和高級IP到優化RTL的自動流程

由于Mathworks的MATLAB®環境能夠在極高的抽象層級上進行簡潔地行為表達,現已被廣泛地用于算法探索和設計。在這種環境下開發的M語言模型通常在RT 層級 (RTL)下被進行重新編碼和重新驗證,有些情況下用C/C++進行實施和驗證。與效率低下和容易出錯的人工重新編碼流程不同,Synphony HLS直接從高層次的M語言編碼和Synphony HLS — 優化的IP模型庫中創建可執行的RTL和C模型。通過采用獨特的約束驅動的定點傳播功能,設計師們可以快速和直觀地從高層次浮點M碼的可綜合子集中獲得定點模型。然后Synphony HLS引擎將合成已從架構上進行了優化的RTL,以滿足面積、速度和功耗目標。Synphony HLS允許設計師們能夠保留他們喜歡的算法建模語言,無需重新編碼和重新驗證模型,從而確保了早期的系統級別的驗證和核查。

評論