克服FPGA I/O引腳分配挑戰(08-100)

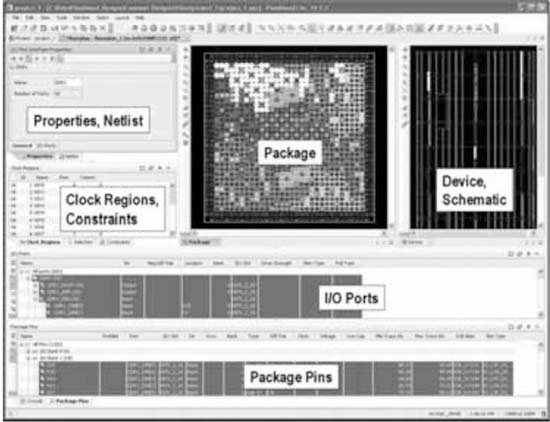

還可利用PinAhead布局設計中其它與I/O相關的邏輯,如BUFG、BUFR、IODELAY、 IDELAYCTRL和DCM。 利用PlanAhead中的“Find”命令,可以方便地定位這些對象和布放點。 要想有選擇地察看的擴展邏輯和邏輯連接,請使用工具中的原理圖視圖(“Schematic” view)。

本文引用地址:http://www.104case.com/article/91695.htm通過在PlanAhead軟件中的某個視圖中選擇特定的I/O相關邏輯并將其拖動到器件視圖(Device view)中的選定位置,就可以鎖定其布局。

PlanAhead軟件將會自動判斷,僅允許將有關邏輯放在合適的位置。 在拖動設計中的邏輯對象時,動態光標會顯示出適當的布局位置。

步驟4: 為最終核簽(Sign-Off)運行DRC和WASSO

一旦完成引腳分配,就可利用 PinAhead豐富的DRC規則來進行核簽前的DRC檢查,保證在運行PlanAhead軟件實施工具前設計是無錯的。 工具中的眾多I/O和時鐘相關規則可保證I/O布局是合法的。 可利用PlanAhead的DRC對話框來選擇相應的規則。

如果工具發現違反規則的情況,將會顯示帶有錯誤信息的DRC結果表。 選擇相應的錯誤信息可以更進一步入地了解有關情況。

PlanAhead還提供了加權平均同步轉換輸出(WASSO)分析功能,可幫助識別引腳分配引起的潛在信號完整性問題。 為工具提供PCB設計的寄生參數特性,PlanAhead軟件將會分析不同的I/O組以及其近鄰,并報告每一I/O組的利用情況和狀態。

步驟5: 導出I/O引腳分配數據

你可以將I/O端口列表和封裝引腳信息從PlanAhead軟件導出為CSV格式文件、HDL頭或UCF文件。 CSV文件包括有關器件封裝引腳的所有信息,以及與設計相關的I/O引腳分配和配置。 列表中的封裝引腳部分是數據表中定義I/O端口的很好起點。

你還可以利用該數據表自動生成設計小組開始PCB布局所需要的PCB原理圖符號。 然而,有時這些符號對于原理圖來說太長了,可能需要將它們縮短為幾個符號。 利用PinAhead中的創建的接口組可以快速做到這一點。

以原理圖符號形式提供這些I/O引腳配置為PCB設計人員開始PCB布局提供了很好的基礎。 因為如果在引腳分配的最初就考慮到PCB接口,那么最很可能與最終的引腳配置比較接近。

如果確實需要改變引腳來方便布線,那么改變也比較容易,因為需要改變的引腳可能已經在I/O組內了。 這種方法不會對FPGA設計造成太大的影響。 通過在PCB和FPGA設計人員之間傳遞修改過的引腳布局數據表或UCF文件,可以保證兩個部分之間的任何修改是同步的。

為防止信號噪聲以及支持某些FPGA功能,你還可能希望將未用的引腳或特定配置的引腳連接到VCC或GND。 賽靈思目前正在致力于在PinAhead的下一版本中提供這一功能。通過一個界面方便FPGA設計人員指導此類引腳,并在輸出的CSV數據表中包含相應的引腳連接。 這樣PCB設計人員就可以更容易識別相關引腳并正確連接之。

未來,隨著FPGA集成更復雜的功能以及使用更先進的封裝,發展可靠的FPGA和PCB引腳布局方法勢在必行。 PinAhead Lite在幫助實現基于協同設計理念的引腳布局策略方面已經能夠提供很大幫助,但我們仍然已經在致力于改進這一工具以幫助設計人員更好地應對引腳布局方面的挑戰。

圖 2 PinAhead 環境

評論