克服FPGA I/O引腳分配挑戰(08-100)

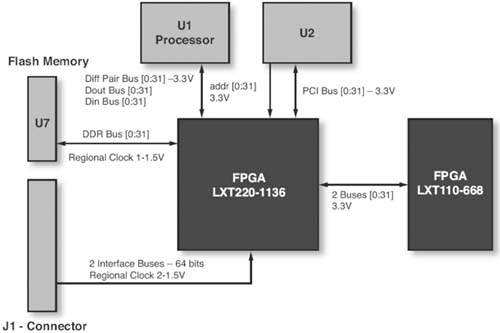

圖1 PCB連接圖

步驟2: 定義引腳布局要求

一旦了解了主要的FPGA接口并創建了物理布局的原型,就可以定義引腳布局了。 有些設計人員喜歡使用包含所有I/O信號數據表來保持與引腳的對應。 你可以按電壓、時鐘、接口或總線對它們進行分組。 這一方法確實非常有用,因為它可幫助你將信號組合成組,從而在分配引腳時可以按組進行。 這一階段,你還會發現為了實現最優PCB布線,有些關鍵接口必須置于器件的某個邊,或者利用外部物理引腳。

在考慮到FPGA和PCB要求并確定了主要的接口位置以后,下一步是根據所有這些條件將引腳分配給I/O組。 這也是真正開始工作的地方。 在當前的設計流程中,引腳分配時一項耗費時間的任務,在解決任何性能和信號完整性問題的過程中可能會涉及許多嘗試和錯誤。 傳統上,設計人員都是徒手畫圖來完成這項任務的,因為EDA和芯片供應商沒有提供幫助設計人員將FPGA和PCB引腳布局可視化的工具。

但現在賽靈思公司提供了相應的工具。 在ISE Foundation軟件工具10.1版本中包含的PlanAhead Lite是PlanAhead設計、分析和平面布局工具的簡化版。 其中包括的針對PCB 和 FPGA設計的PinAhead的工具使得I/O引腳配置更為容易。

這里我們不打算詳細介紹該工具的所有細節,而只是看一下如何將其用于I/O引腳分配。 如果你希望了解PinAhead的更詳細信息,包括視頻展示和教程,請訪問 www.xilinx.com/planahead。

步驟3: 利用PinAhead進行引腳分配

PinAhead環境提供了一組不同的視圖。利用這些視圖可以幫助完成I/O端口信息與物理封裝引腳或裸片I/O盤(Pad)的對應和分配(圖2)。

PinAhead的圖形環境與PlanAhead類似,在器件視圖中清晰地顯示出芯片上的I/O盤和相關資源,并在封裝視圖中顯示出物理器件引腳。 視圖同時顯示出I/O端口和物理引腳信息,這樣可以通過交叉選取來試探邏輯設計和物理器件資源的對應。

評論