DDR2 SDRAM介紹及其基于MPC8548 CPU的硬件設計(08-100)

——

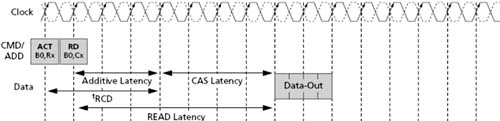

針對這個問題,DDR2 SDRAM做了改進。DDR2 SDRAM允許RD AP命令提前發出,甚至可以緊跟ACT命令發出,但是要等待一個Additive Latency(即AL,附加延時)后,該RD AP命令才能執行。如圖3所示。

本文引用地址:http://www.104case.com/article/91686.htm

圖3 引入附加延遲AL的DDR2 SDRAM讀取模式【1】

在圖3中,AL設置為tRCD-1,此時,可以實現ACT和RD AP命令背靠背的發出,只不過,DDR2 SDRAM需要抑制RD AP命令,直到AL延時滿足后才能執行。

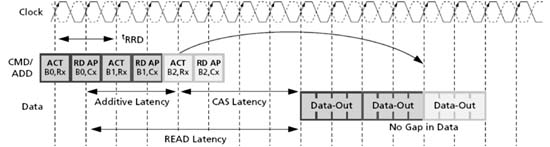

圖4 引入AL后的多Bank數據讀取

如圖4,引入AL并設置AL為tRCD-1后,對于多個Bank數據讀取,輸出數據流之間不再出現間隙。

這種為了避免ACT命令和RD AP命令沖突而提出的技術就叫做Posted CAS技術。其本質就是將CAS#信號的使能時間段(即RD AP命令)直接插入到緊跟RAS#信號的使能時間段(即ACT命令)之后,雖然讀和寫操作并沒有得到提前,總的延遲時間也沒有發生改變,但引入這種技術后,可以避免在多Bank操作中的一個Bank的CAS#信號和其他Bank的RAS#信號發生沖突,從而提高了存儲芯片的使用效率。

可以通過配置DDR2 SDRAM芯片內部的EMR寄存器的第3~5位,將附加延時AL配置為0~5個時鐘周期。

上拉電阻相關文章:上拉電阻原理

評論