DDR2 SDRAM介紹及其基于MPC8548 CPU的硬件設計(08-100)

DDR2 SDRAM引入的新技術

本文引用地址:http://www.104case.com/article/91686.htmDDR2(Double Data Rate 2,兩倍數據速率,版本2) SDRAM,是由JEDEC標準組織開發的基于DDR SDRAM的升級存儲技術。 相對于DDR SDRAM,雖然其仍然保持了一個時鐘周期完成兩次數據傳輸的特性,但DDR2 SDRAM在數據傳輸率、延時、功耗等方面都有了顯著提高,而這些性能的提高,主要來源于以下技術的提升:ODT,Post CAS,4n數據預取,封裝等。

* ODT

ODT(On-Die Termination),即芯片內部匹配終結。

在DDR SDRAM應用中,需要通過大量的外部電阻上拉到VTT電平(1.25V)以實現信號匹配,以16位芯片為例,以下信號需要通過這種方式進行匹配:CK,CK#,DQ[15:0],LDQS,UDQS, ADDR[10:0],RAS#,CAS#,WE#,即一片芯片需要34個外部上拉電阻,極大的占用了寶貴的PCB面積。同時,由于DQ[15:0],LDQS,UDQS等信號是雙向信號,即讀和寫時,對匹配電阻的位置有不同要求,因此在電阻布局時很難在兩個方向上同時實現最佳的信號完整性。

在DDR2 SDRAM中,采用ODT技術將許多外部的匹配電阻移到芯片內部從而節省了大量的PCB板上面積。另外,ODT技術允許存儲控制器(如下文的MPC8548 CPU)通過配置DDR2 SDRAM的內部寄存器以及控制ODT信號,來實現對匹配電阻的值及其開關狀態進行控制,從而可以實現讀,寫操作時最佳的信號完整性。

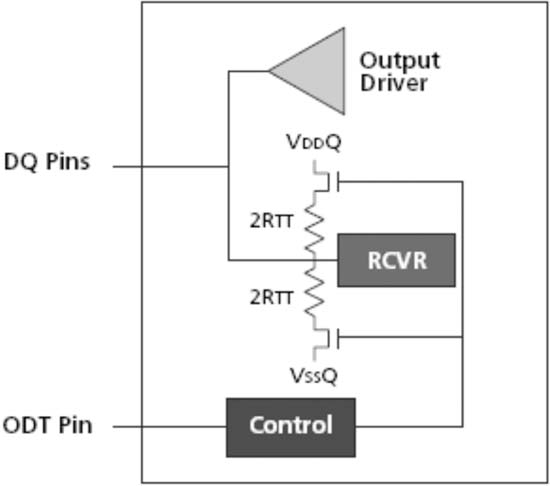

圖1 ODT功能圖

DDR2 SDRAM芯片提供一個ODT引腳來控制開或關芯片內部的終結電阻。在只有一個DDR2 SDRAM芯片作為存儲器控制器的負載的情況下,寫操作時,由于DDR2 SDRAM作為接收端,所以ODT引腳為高電平以打開芯片內部終結電阻;讀操作時,由于DDR2 SDRAM作為發送端,所以ODT引腳為低電平以關閉芯片內部終結電阻。其中,ODT引腳的狀態由存儲器控制器(如MPC8548)來控制。

上拉電阻相關文章:上拉電阻原理

評論