數字RF存儲器用混合信號ASIC(05-100)

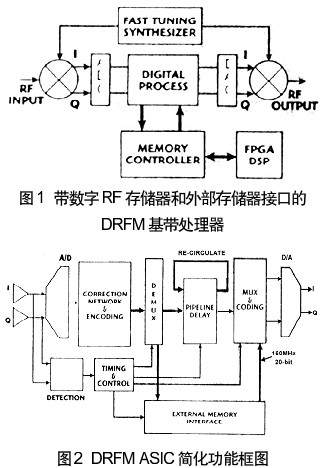

數字RF存儲器(DRFM)用于現代脈沖壓縮雷達中合成相干信號的再生。DRFM系統有很多不同的實現方法。圖1示出1個特殊的類型,它是1個雙邊帶,4位,相位取樣系統,它的瞬時帶寬為500MHz。采用0.18祄 CMOS 工藝制造的混合信號專用集成電器(ASIC)可實現系統的基帶元件,這包括相位取樣電路、數字處理、信號重建和數/模輸出。

本文引用地址:http://www.104case.com/article/91407.htmASIC設計

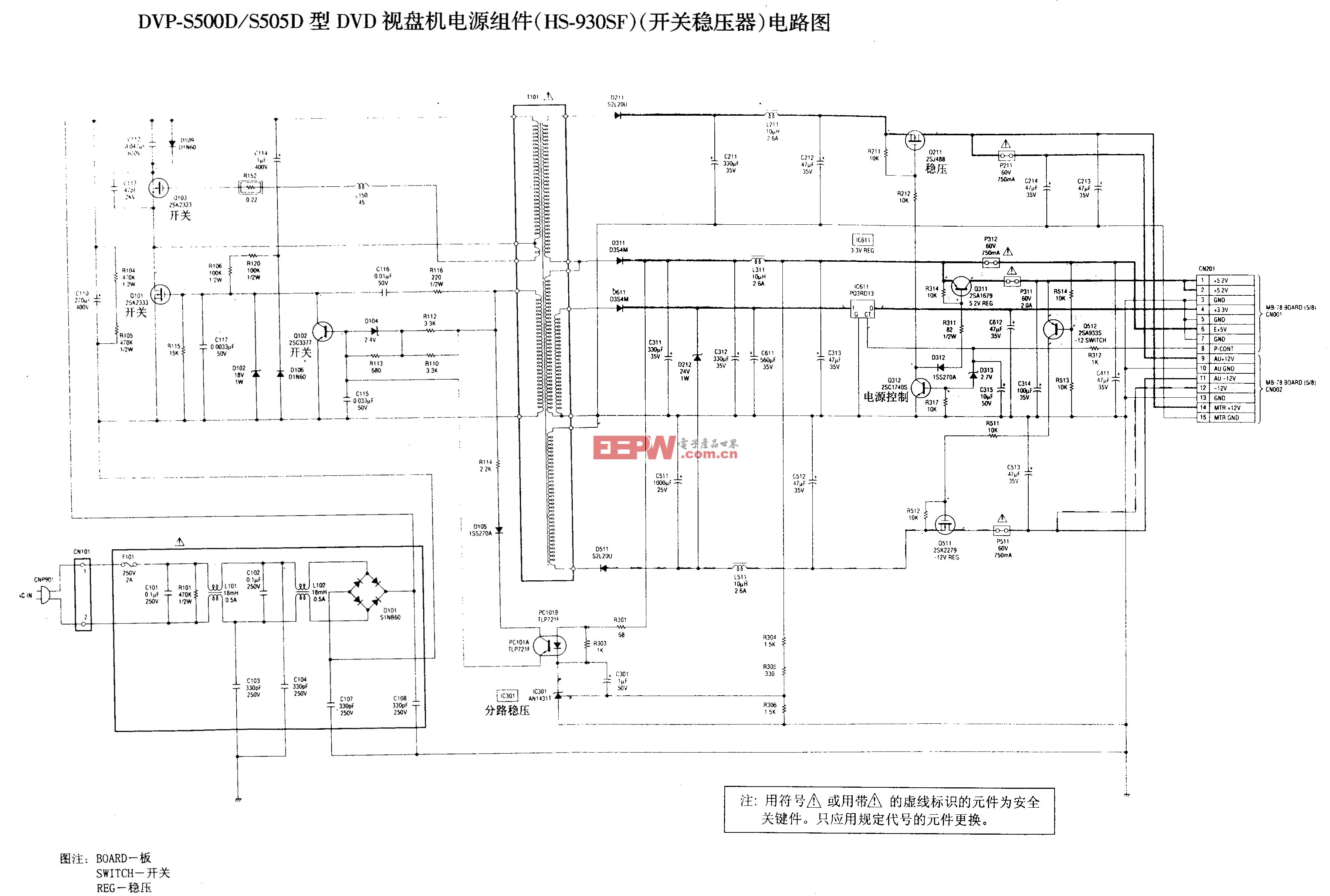

圖2示出LNX公司的LNX DRFM ASIC框圖。前置放大器級放大、緩沖、電平變換輸出到適合于接口數字邏輯電路。輸入帶寬是250MHz,用I和Q輸入提供500MHz瞬時帶寬。用高速比較器以高達640MHz取樣I和Q輸入,而用查表進行誤差校正和編碼為4位相位值(分辯率為22.5H緩蟠媧⑹縈糜詿硨投臉觥S孟轡皇鶯駝?余弦查表重建信號。

編碼后,數據進入信號分離單元,它以1/4取樣率分發給20位總線,以便于存儲在外部存儲器。另外,數據饋入下一個延遲線單元。此單元實現兩個功能:以固定的增益延遲數字化的信號或用于信號重建的數據再循環。重建或再循環使得重放的CW信號具有記錄信號的正確相位和頻率特性。最小吞吐量時間延遲小于25ns。

外部存儲器接口工作在160MHz并執行數據存儲和讀出的分離。全雙工工作允許與從前存儲信號的讀出和傳輸同時取樣和存儲信號。數據信號電平是3.3V CMOS,時鐘是差分LVDS。此ASIC為外部存儲提供所有的定時和控制。外部存儲器,FPGA或DSP處理系統可用于存儲和/或處理所記錄的波形。

ASIC包含維護再循環信號相位相干所必須的定時。定時也提供到外部電路來維持記錄信號的相干。

它還包含另外的附加電路,如偽隨機噪聲(PN)產生器和頻率測量功能單元。PN噪聲產生器可用于在輸出信號上增加偽隨機噪聲。頻率測量單元可測量輸入信號的頻率,用累加△相位測量可達10位精度,根據脈沖寬度可自動調節頻率測量的分辯率。

評論