DSP+FPGA在高速高精運動控制器中的應用

運動控制卡已經在數控機床、工業機器人、醫用設備、繪圖儀、IC電路制造設備、IC封裝等領域得到了廣泛運用,取得了良好的效果。目前運動控制卡大部分采用8051系列的8位單片機,雖然節省了開發周期但缺乏靈活性,難以勝任高要求運作環境,而且運算能力有限。

DSP的數據運算處理功能強大,即使在很復雜的控制中,采樣周期也可以取得很小,控制效果更接近于連續系統。把DSP與PC的各自優勢結合將是高性能數控系統的發展趨勢。本運動控制器采用TI公司的高性能浮點DSP作為主控芯片,通過ISA接口與PC協調并進行數據交換,以PC計算機作為基本平臺,以DSP高速運動控制卡作細插補、伺服控制的核心,對直線電機的運動進行控制,取得了良好的實際應用效果。

1 高速高精運動控制卡的主要硬件構成

本運動控制系統的任務是控制直線電機的運動,要求4軸輸入和4軸輸出,采用光柵尺對輸入計數,16位并行高速DA輸出,運動定位精度要求達到10nm,響應時間<100ns。

高速直線電機是本系統的控制對象,它具有加速快(a>10g),運動速度高(v>300mm/s)的特點。要求控制系統有足夠短的響應時間(<100ns)和足夠高的定位精度(10nm級),因而系統的核心CPU的處理能力及運算能力必須滿足高速要求;此外,直線電機運動定位的核心是高精度的反饋控制裝置。直線電機的反饋控制裝置是光柵尺和高精度脈沖計數器,光柵尺發出與運動距離成線性關系的脈沖數,脈沖計數器的計數值表示直線電機當前的運動位置。經計算,計數長度為28位的計數器才能滿足定位的精度要求,同時計數頻率很高。一般的通用計數器參數無法達到,所以設計一個特殊計數器是必要的。為了方便設置目標點的運動參數,使運動控制卡具有比較好的人機交互功能,系統必須具有與PC機通信的功能。

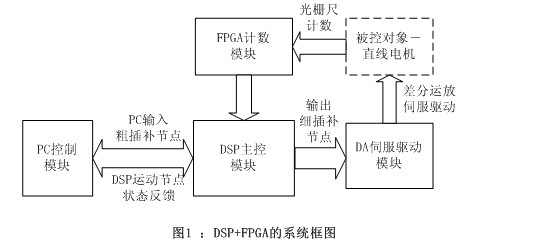

綜合考慮上述要求,系統的設計采用DSP+FPGA的形式,由DSP主控芯片作為中央處理模塊,FPGA作為反饋計數模塊且負責板上的部分邏輯譯碼工作,PC通信接口模塊采用雙口RAM,輸出模塊用D/A轉換器實現,如圖1所示。

1.1 DSP模塊

基于DSP的運動控制系統一般采用TI公司的TMS320C24x系列芯片,但24x系列是16位定點處理器,運算能力有限。不能滿足本系統規劃的高速高精要求,為此,我們選用了TI公司的TMS320C32 DSP作為主控芯片。

TMS320C3X系列芯片是美國TI公司推出的第一代浮點DSP芯片,具有豐富的指令集、很高的運算速度、較大的尋址空間和較高的性價比,在各領域得到了廣泛的應用。TMS320C32是TMS320系列浮點數字信號處理器的新產品,在TMS320C30和TMS320C31的基礎上進行了簡化和改進。在結構上的改進主要包括可變寬度的存儲器接口、更快速的指令周期時間、可設置優先級的雙通道DMA處理器、靈活的引導程序裝入方式、可重新定位的中斷向量表以及可選的邊緣/電平觸發中斷方式等。

對TMS320C32的開發可以用匯編語言,也可以用C語言。使用匯編語言的優點在于運行速度快、可以充分利用芯片的硬件特性,但開發速度較慢,程序的可讀性差;而C語言的優勢在于編程容易、調試快速、可讀性好,可以大大縮短開發周期,但C語言對于其片內的沒有映射地址的特殊功能寄存器不能操作,如IF和IE,AR0~AR7等。

1.2 FPGA模塊

該部分主要功能為一個4通道的針對光柵尺的脈沖計數器,此外,還承擔部分地址譯碼的工作。但由于脈沖計數頻率高,計數量大,所以必須選擇高容量、高性能的可編程邏輯器件。

ALTERA FLEX(Flexible Logic Element Matrix)10K 系列FPGA,規模從一萬門到十萬門,可提供720~5392個觸發器及6144~24576位RAM,提供30ns、40ns及50ns等幾個速率等級,可適應18~105MHz的信號處理速率。ALTERA FLEX10K系列FPGA主要由輸入輸出單元IOE、掩埋陣列EAB、邏輯陣列LAB及內部連線組成。EAB是在輸入和輸出端口加有寄存器的RAM塊,其容量可靈活變化。所以,EAB不僅可以用于存儲器,還可以事先寫入查表值來用它構成如乘法器、糾錯邏輯等電路。當用于RAM時,EAB可配制成多種形式的字寬和容量。

LAB主要用于邏輯電路設計,一個LAB包括8個邏輯單元LE,每一個LAB提供4個控制信號及其反相信號,其中兩個

可用于時鐘信號。每一個LE包括組合邏輯及一個可編程觸發器。觸發器可被配成D,T,JK,RS等各種形式。IOE提供全局的時鐘及清零信號輸入端口,還提供具有可編程性的各種輸入輸出端口,如低噪聲端口、高速端口等。

FLEX10K系列芯片是ALTERA公司新近推出的PLD產品。與ALTERA公司先前推出的MAX7000系列EPLD相比,FLEX10K(以下簡稱10K)系列具有更加豐富的內部資源(最多可達10萬門),更加充裕的可配置的I/O管腳(最多達406條)。再加上其低廉的價格,使得10K系列芯片受到越來越多用戶的歡迎。

基于以上原因,我們在本方案中采用ALTERA FLEX10K10,并且考慮到以后設計的連續性,我們可以無需更改硬件電路,就可以更換性能更高的、相同尺寸、相同管腳配置的ALTERA FLEX10K20。

1.3 PC通信接口模塊

該模塊選用16位的ISA總線與PC相連,CY7C133雙口RAM用作數據緩沖。

ISA總線的使用十分靈活、方便,而且I/O操作比較簡單。雖然ISA總線的引腳多但并不是都要用到的,關鍵是幾個固定引腳的應用,例如:I/O CH RDY、I/OR、I/OW、ALE、數據線和地址線,結合起來實現通信。

在本系統中,雙口RAM的 PC端地址線并沒有直接采用ISA過來的地址線,而是由FPGA內部地址計數器給定。這是因為,ISA總線上大部分地址都已經被PC系統分配好,直接把2K的雙口RAM數據空間映射到ISA總線上并不現實;而且控制系統與PC交換的數據基本上是一系列加工點的坐標參數,采用順序訪問對性能沒有影響。因此采用地址計數器方式的順序訪問,完全能夠達到設計的要求。

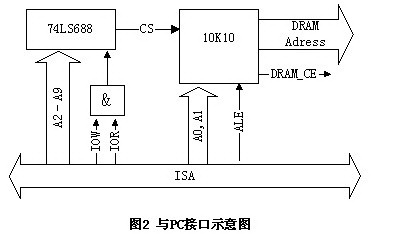

具體做法是:ISA地址線的A2~A9接到地址比較器74LS688,與設定好的地址作比較,74LS688的片選信號由ISA的IOR和IOW的“與”提供(IOR和IOW在ISA總線訪問端口時低有效),A0,A1接到FPGA,用于選擇FPGA內部4個功能不同的寄存器。ISA的ALE用于觸發FPGA 內部邏輯功能,鎖存ISA總線過來的信號,如圖2所示。

當訪問地址清零寄存器時,地址計數值清零;當訪問地址增加寄存器時,地址計數值增加“1”。如此類推,訪問不同的寄存器就對地址計數值完成不同的操作,把地址計數值直接作為地址送給雙口RAM,就可以實現ISA總線訪問雙口RAM了。

1.4 輸出模塊

輸出模塊采用模擬輸出,經外部放大驅動電機的方案。D/A轉換芯片選擇DAC7744。

DAC7744是高性能的4通道16位高速D/A,主要特點如下:

● 輸出通道:獨立4 路

● 輸出信號范圍:0~5V;0~10V;±5V;±10V

● 輸出阻抗:≤2Ω

● D/A轉換器件:DAC7744

● D/A轉換分辨率:16位

● D/A轉換碼制:二進制原碼(單極性) 二進制偏移碼(雙極性)

● D/A轉換時間:≤1μs

● D/A轉換綜合誤差:≤0.02% FSR

● 電壓輸出方式負載能力:5mA/路

pid控制器相關文章:pid控制器原理

評論