基于FPGA的高速PID控制器設計與仿真

在CNC(電腦數控)加工、激光切割、自動化磨輥弧焊系統、步進/伺服電機控制及其他由電機控制的機械組裝定位運動控制系統中,PID控制器應用得非常廣泛。其設計技術成熟,長期以來形成了典型的結構,參數整定方便,結構更改靈活,能滿足一般控制的要求。

本文引用地址:http://www.104case.com/article/82229.htm此類運動控制系統的被控量常為速度、角度等模擬量,被控量與設定值之間的誤差值經離散化處理后,可由數字PID控制器實現的控制算法加以運算,最后再轉換為模擬量反饋給被控對象,這就是PID控制中常用的近似逼近原理。

采用這種結構設計的控制系統,其性能只能與原連續控制系統性能接近而不會超過,逼近的精度與被變換的連續數學模型大小及采樣周期長短有關[1]。特別是在高速運動控制的情況下,采樣周期的影響更大,采樣周期相對較長時,逼近程度才較好,但是對PID控制算法的運算速度及回路的調節時間等也提出了更高的要求。

可編程邏輯器件FPGA的邏輯門數為5000~200萬個,屬于大規模甚至超大規模邏輯器件,其工作頻率最高可達250MHz。因此,無論從編程規模還是工作速度上,完全可以用來實現高速PID控制器。本設計使用Altera公司的Cyclone系列FPGA器件EP1C3作為硬件開發平臺,對運動控制中常用的增量式數字PID控制算法進行優化處理,提高了運算速度和回路的調節時間。

1 增量式數字PID控制算法的FPGA實現

經典PID控制方程為:

![]()

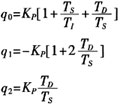

式中,KP為比例放大系數;K1為積分時間常數;KD為微分時間常數。數字PID控制算法的實現,必須用數值逼近的方法。當采樣周期相當短時,用求和代替積分,用差商代替微商,使PID算法離散化,將描述連續一時間PID算法的微分方程離散化、差分、歸并處理后可得:

![]()

從(2)式可以看出,增量式數字PID算法,只要儲存最近的三個誤差采樣值e(k)、e(k-1)、e(k-2)就足夠了。實現此增量式數字PID控制算法的結構圖如圖1所示。

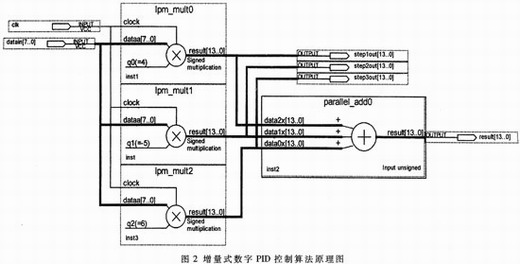

圖1中虛線框以內的結構是三個具有移位功能的乘法器,可以使用Altera公司提供的經過嚴格測試和優化處理的宏功能模塊LPM_MULT(M0~M2)實現。LPM_MULT是一個可定制位寬的加法/乘法器,在此,定制誤差輸入值e(k)的位寬為8bit,另一常量乘數q0、q1、q2為整定后的PID控制器的控制參數,位寬為6bit,乘法器輸出結果位寬為14bit。QuartusII中的原理圖如圖2所示。

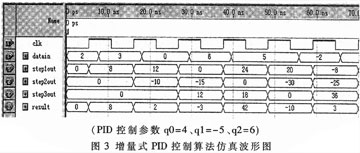

LPM_MULT宏功能模塊還可以定制運算結果輸出時等待同步脈沖(clock)的個數,這就是LPM_MULT的流水線輸出功能。圖2中指定lpm_mult0、lpm_multl、:lpm_mult2的等待時間依次為1、2、3個同步脈沖,這種設計自然地實現了移位相乘操作;同時利用乘法器的流水線功能,提高了乘法運算的速度。優化后的功能仿真波形如圖3所示。

由圖2、圖3可見,在第K個流水線推進時鐘信號clk的上跳沿,lpm_mult0輸出當前時刻下的乘積運算結果steplout,lpm_multl輸出K一1時刻下的乘積結果step2out,lpm_mult2輸出K-2時刻下的乘積結果step3out,并行加法運算部件parallel_add的輸出值為result=steplout+step2out+step3out。

2 通用模/數、數/模轉換器的設計與仿真

為了不失系統的通用性和可擴展性,參照ADI公司8bit、半閃爍型A/D轉換器AD7822的時序圖,設計了通用A/D轉換部件typical_ADC實現系統的模/數轉換仿真功能。typical_adc部件是一個理想化的A/D轉換芯片,主要由一個8位地址計數器和一個存放正弦數據的ROM構成,它模擬正弦信號的采樣、量化過程,采樣周期只與系統的工作時鐘有關[2]。

相對于模/數轉換而言,數/模轉換的控制信號要少一些,時序要求更簡單。參照TI公司14位D/A轉換芯片DAC8806的功能表,設計了一個通用D/A轉換部件typical_dac實現系統的數/模轉換仿真功能。為了形式化地表示系統的D/A轉換過程,typical_dac只是對PID算法的輸出量△u(k)做了一個奇偶校驗運算,VHDL語言描述如下:

ARCHITECTURE behav OF typical_dac IS

BEGIN-當轉換控制信號wr為低電平時輸出各位異或值,否則輸出高阻態

uout<=(datain(0)XOR datain(1)XOR datain(2)XOR datain(3)XOR datain(4)XOR datain(5)XORdatain(6) XOR datain(7)X0R datain(8)XOR datain(9):XOR datain(10)XOR datain(11)XOR datain(12)XOR datain (13)XOR`1`)WHEN wr=`0`ELSE`z`;END behav;;

3 工作控制狀態機的設計

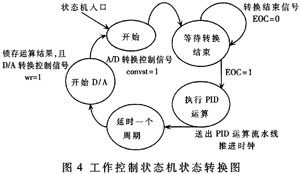

典型的數字PID控制系統由A/D轉換、PID控制算法和D/A轉換三個關鍵環節構成。為了協調三個環節之間的工作流程,系統工作控制部件必不可少。純硬件數字系統的順序控制有多種方案可選,如單片機輔助控制、嵌入式CPU軟核控制、脈沖計數控制等等,但都難以兼顧系統的高速控制和靈活擴展。在高速運算和控制方面,有限狀態機具有以上幾種控制方式難以超越的優越性。

從狀態機的信號輸出方式上分,有Moore型和Mealy型兩類狀態機。從輸出時序上看,前者屬于同步輸出狀態機,而后者屬于異步輸出狀態機。Mealy型狀態機的輸出是當前狀態和所有輸入信號的函數,它的輸出是在輸入變化后立即發生的,不依賴于時鐘的同步[2]。

Moore型狀態機的輸出則僅為當前狀態的函數,這類狀態機在輸入發生變化時還必須等待時鐘的到來,時鐘使狀態發生變化時才導致輸出的變化,所以比Mealy機要多等待一個時鐘周期,但是能有效避免毛刺現象。本設計所用的狀態機為單進程Moore型狀態機。狀態轉換如圖4所示。

4 系統實現與功能仿真

整個PID控制器的系統設計采用自頂向下的設計方法和模塊化的設計思想,即先由PTD控制器的自然語言描述得到VHDL的系統行為描述,然后對系統分解為誤差A/D變換部件、PID運算部件、控制增量D/A變換以及協調三者的控制狀態機等四個主要模塊。

Altera公司專用EDA軟件QuartusII支持原理圖與VHDL語言混合輸入設計方式,除PID運算部件采用原理圖輸入設計方式以外,其余三個部件均采用VHDL輸入設計方式。系統仿真時,如果將系統的最高工作速率設定為120MHz,則采樣速率為24MHz。功能仿真波形圖如圖5所示。

通過對增量式數字PID控制算法的優化處理,顯著提高了系統的工作速度。仿真結果表明,擁有較低轉換速率的A/D變換技術成為提高系統運行速度的瓶頸。就本設計采用的閃爍型A/D器件而言,減少狀態機等待A/D轉換結束信號EOC(見圖4)的時間,即提高A/D轉換的速率是提高系統整體工作速率的關鍵。

本設計中所采用的增量式數字PID控制算法的設計思想可以應用到有限長單位脈沖響應(FIR)濾波器和無限長單位脈沖響應(ⅡR)濾波器的FPGA設計中,并且同樣可以使用流水線優化技術以提高工作速度。同時,由于PLD設計和專用ASIC設計的通用性,在PLD設計平臺上所完成的設計可以很自然地過渡到專用ASIC的設計工作中,進一步提高了系統的可靠性和集成度。

評論