深入研究DDR電源(07-100)

我們將深入研究需要這些電壓的原因。

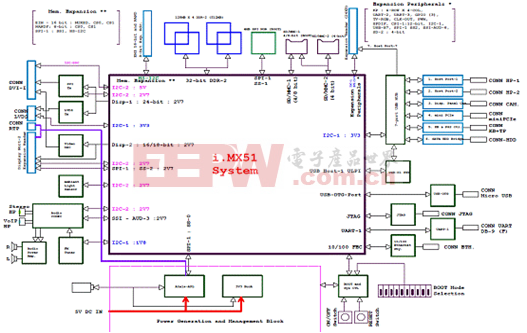

本文引用地址:http://www.104case.com/article/81733.htm盡管DDR存儲器在無需加倍時鐘頻率的情況下使數據傳輸率加倍,避免了PC板設計和布局的復雜性,但它要求有更嚴格的dc穩壓、更高的電流和對端電源電壓(VTT)和存儲總線電壓(VDD)緊密的跟蹤。新型串聯端接邏輯(SSTL)拓樸的引入是用于提高抗噪性、增加電源抑制并使用更低的電源電壓以降低功耗。

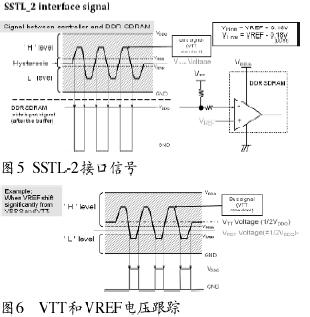

JEDEC標準JESD8-9A(用于SSTL_2)和JESD8-15(用于SSTL_18)定義了VDDQ、VTT和VERF以及驅動器/接收器規格以分別滿足在VDDQ= 2.5 V (用于 DDR1) 和VDDQ = 1.8 V (用于 DDR2)時的噪聲容限。下面,我們看看這種接口以更好的理解VREF和VTT的需要。

SSTL接口

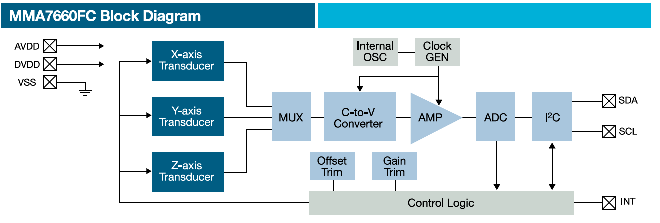

圖3顯示了DDR存儲器的新型串聯端接邏輯(SSTL)拓樸。

SSTL_2的接口具有下述特性:

·DDR存儲器具有推挽式的輸出緩沖,而輸入接收器是一個差分級,要求一個參考偏壓中點,VREF。因此,它需要一個能夠提供電流和吸收電流的輸入電壓端。

·在驅動芯片集的任何輸出緩沖器和存儲器模塊上相應的輸入接收器之間,我們必須端接一個布線跟蹤或帶有電阻器的插頭。

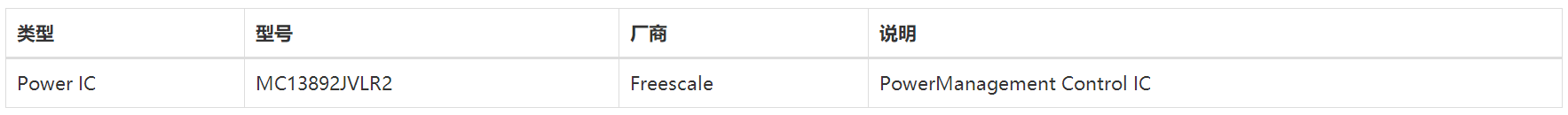

VTT電源的電流流向隨著總線狀態的變化而變化。因此,VTT電源需要提供電流和吸收電流 (source & sink),如圖4中紅色和藍色箭頭所示。

由于VTT電源必須在 1/2 VDDQ提供和吸收電流,因此如果沒有通過分流來允許電源吸收電流,那么就不能使用一個標準的開關電源。而且,由于連接到VTT的每條數據線都有較低的阻抗,因而電源就必須非常穩定。在這個電源中的任何噪聲都會直接進入數據線。

圖5詳細闡述了信號如何流過SSTL_2接口。

存儲器相關文章:存儲器原理

評論