深入研究DDR電源(07-100)

DDR存儲器的發(fā)展歷程

本文引用地址:http://www.104case.com/article/81733.htm由于幾乎在所有要求快速處理大量數(shù)據(jù)(可能是計算機、服務(wù)器或游戲系統(tǒng))的應(yīng)用中都要求具有RAM(隨機存儲器),因而DDR存儲器也變得日益重要,其應(yīng)用也更加廣泛。自問世以來,RAM就已經(jīng)變得至關(guān)重要,主要因為它是一種能夠保存易失性信息的存儲器,并且可以以一種更快速、更直接的方式存取信息。當在數(shù)據(jù)計算的世界里談及系統(tǒng)速度和效率時,這一點顯得尤為重要。

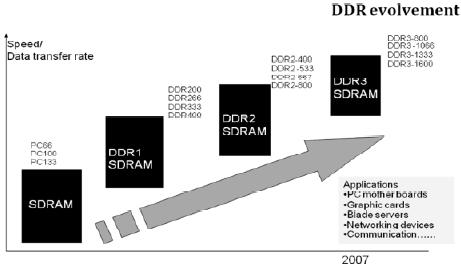

DDR SDRAM(雙數(shù)據(jù)速率同步動態(tài)隨機存儲器),其可以通過在時鐘周期的上升和下降沿上分別提取數(shù)據(jù)而使數(shù)據(jù)率加倍,現(xiàn)在看來它正發(fā)展成為最先進的RAM芯片集。這與以往的SDR SDRAM大不相同,因為后者僅能在時鐘周期的一個邊沿上提取數(shù)據(jù)。從圖1可以看出,DRAM正在向著速度和數(shù)據(jù)傳輸率都不斷提高的方向發(fā)展。

近些年來,CPU時鐘頻率經(jīng)歷了指數(shù)增長,從而為RAM存儲器的時鐘頻率增長提供了動力。

在1997年,SD RAM在市場亮相,它可以取代DRAM和SRAM兩種存儲器并提供更快的時鐘速率。這主要源于SDRAM具有更簡捷的通信協(xié)議;所有指令、地址和數(shù)據(jù)都由一個單獨的時鐘信號控制并且工作在突發(fā)模式,可以在66MHz的時鐘頻率下突發(fā)一系列數(shù)據(jù)字。在1998年,SD RAM頻率已經(jīng)增長到100MHz 的突發(fā)脈沖速率。

在1999年,英特爾和AMD間的企業(yè)競爭升級,在CPU時鐘速度方面也不例外。處理器行業(yè)的蓬勃發(fā)展進一步加大了CPU時鐘速度與其它系統(tǒng)組件間的差距。在此期間,盡管存儲器總線速度已經(jīng)全力達到了133MHz,但卻仍然遠遠落后于CPU所能完成的速度,因此,總的來說,這也成為提高整體應(yīng)用速度的瓶頸。

為了解決這個問題,DDR RAM(雙數(shù)據(jù)速率傳輸)的設(shè)計應(yīng)運而生。DDR RAM允許分別在時鐘的上升沿和下降沿上提取數(shù)據(jù),從而加倍了時鐘的有效傳輸速率。例如,一個100MHz的DDR時鐘能夠達到相當于200MHz時鐘頻率的峰值傳輸速率。這就是DDR1技術(shù),其速度可高達400MHz。

下一代DDR,即我們所說的DDR2。DDR2技術(shù)將數(shù)據(jù)傳輸速率從400MHz提升到800MHz,數(shù)據(jù)總線為64位(8字節(jié))。它不能與前一代DDR1存儲器實現(xiàn)物理兼容,這種二代存儲器現(xiàn)在已經(jīng)是由RAM存儲器廠商普遍生產(chǎn)的產(chǎn)品。

存儲器相關(guān)文章:存儲器原理

評論