在FPGA中集成高速串行收發器面臨的挑戰

——

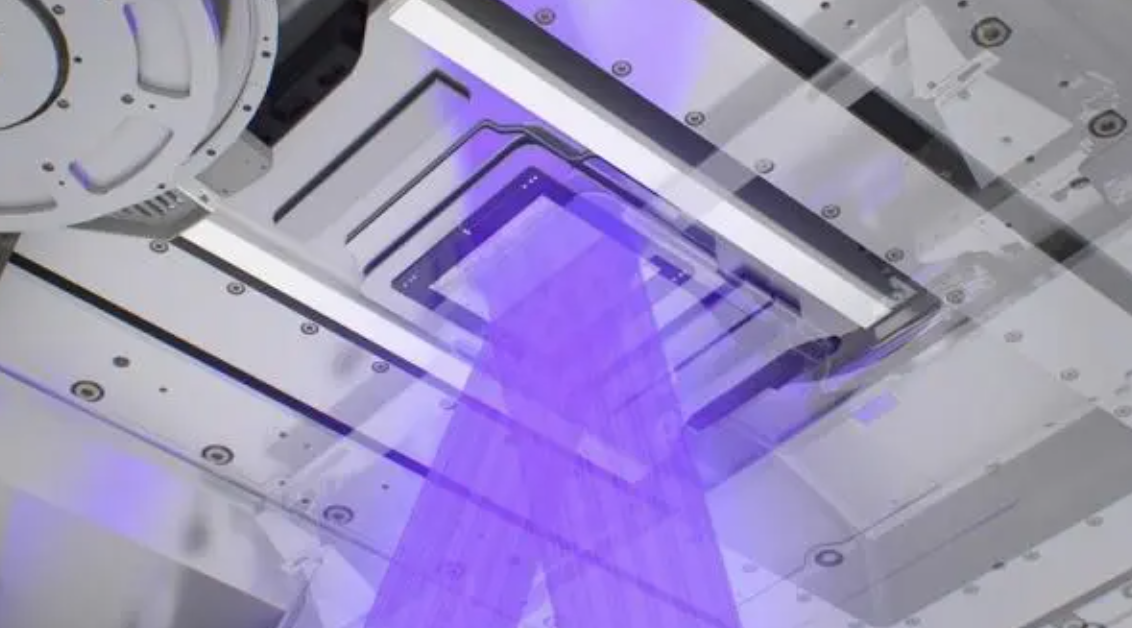

Altera公司對PCI Express,串行Rapid I/O和SerialLite等串行標準和協議的認可,將促進具有時鐘和數據恢復(CDR)功能的高速串行收發器的應用。這些曾在4或8位ASSP中使用的收發器現在可以集成在高端FPGA中。帶有嵌入式收發器的FPGA占據更小的電路板空間,具有更高的靈活性和無需接口處理的兩芯片方案等優勢,因此,采用這種FPGA對電路板設計者是很具有吸引力的選擇。

在FPGA中集成收發器使得接口電路處理工作由電路板設計者轉向芯片設計者。本文闡述在一個FPGA中集成16

評論