下一代FPGA有望實現突破性優勢

定制方法提供了突破性功能

本文引用地址:http://www.104case.com/article/283452.htm為滿足通信、國防、廣播和存儲對帶寬和性能越來越高的需求,為工廠自動化、汽車和消費類便攜式產品提供低成本和低功耗最優解決方案——需要更廣泛專業的知識和工具。這包括,但是不限于:

■ 前沿的制造工藝技術

■ 在不同體系結構和IP上的投入

■ 處理器和可編程架構的高性能集成

前沿工藝

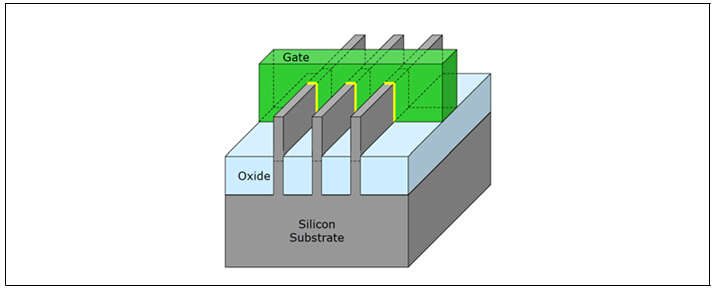

半導體供應商投資于前沿工藝,他們的關鍵優勢是擁有高級工藝技術。例如,新的3-D晶體管技術,它也被稱為三柵極或者FinFET晶體管技術,是工藝技術的新突破(參見圖3)。其晶體管泄漏降低了兩倍,能提高性能,或增強功率。

圖3.三柵極工藝技術

截至2014年第三季度Intel發售了5億多片基于FinFET技術的芯片,表明了其工藝已經成熟,在基于FinFET的技術上有很好的經驗。如果可編程解決方案公司能夠迅速高效的采用這些產品,就能夠大幅度提高性能。而且,客戶需要提高產品性能不僅可以利用這一3-D晶體管技術,而且會受益于今后越來越簡單的工藝。最近發布的Intel 14 nm三柵極工藝提供了這一工藝技術。

事實是,沒有一種工藝技術能夠滿足目前終端設備的各種需求——即使是工藝尺寸最小或者最“先進”的工藝。FPGA和其他可編程SoC產品供應商如果只依靠某一種能夠滿足所有需求的方法,那將對客戶非常不利。

產品及時面市、成本、與其他組件的系統集成和產量等因素會促使采用其他工藝技術。例如,新的工藝節點很可能無法很好的支持高電壓I/O。其他類型的工藝節點在每I/O單位成本上會有較強的優勢。因此,14 nm三柵極工藝是極低功耗實現最佳內核性能的基礎,但并不一定是所有系統應用的最優方案。其他工藝技術能夠完善Intel的14 nm三柵極工藝,例如,TSMC的20SoC和55 EmbFlash,以實現多種系統設計目標。

例如,TSMC的20SoC工藝支持客戶在產品中采用下一代FPGA,在能夠使用14 nm器件之前,就可以投入到大批量寬帶基礎設施市場中。客戶的內核性能得到了提高,與目前大批量應用的功能相似的FPGA相比,系統可以運行在500 MHz以上,其ARM?處理器高達1.5 GHz,而功耗降低了50%。這一20 nm工藝是客戶滿足關鍵目標的基礎,例如,電信、數據中心和其他應用所要求的單位比特成本和每瓦性能。嵌入式閃存工藝等其他工藝支持系統設計人員獲得單位I/O引腳最低成本,支持低功耗解決方案,還可以采用模擬電路和非易失閃存,而這是其他工藝在經濟上無法實現的。

體系結構和IP

為滿足比當今應用高出四倍的帶寬性能需求,應采用更先進的工藝技術。這需要新的邏輯體系結構、新IP,以及新的串行連接等。

下一代體系結構與前沿工藝技術相結合,能夠顯著提高內核性能。例如,Altera最近發布了新的高性能體系結構。與Intel的14 nm三柵極工藝結合后,其內核速率達到了令人吃驚的1 GHz。

這一體系結構極大的提高了數字信號處理(DSP)能力。這些DSP模塊已經應用于FPGA中,而浮點運算的效率會更高。FPGA支持其性能達到每秒10兆次浮點運算(teraFLOPS)。將提供每瓦每秒100 giga浮點運算(GFLOPS),是性能最好、功效最高的解決方案之一,這對于現有DSP或者圖形處理單元(GPU)是無法想象的。這將在金融、能源、云數據分析等高性能、大數據量計算應用中實現突破性功能。

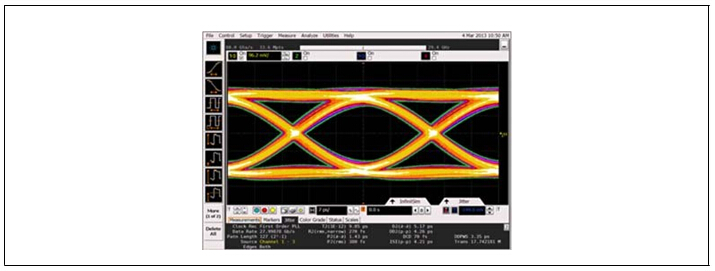

通過提高數據速率、通道數量,包括更多的硬核特性,也將大幅度提高串行帶寬。FPGA公司宣布其下一代收發器技術數據速率將達到56 Gbps。Altera等公司目前提供的單管芯FPGA的收發器數據速率是28 Gbps。單單下一代FPGA的28 Gbps通道數量就將增加四倍,實現下一代100G光接口的多個例化,例如CFP2、CFP4和QSFP28等。采用自適應判決反饋均衡器(DFE)等增強信號調理技術,即使是在電噪聲環境中,收發器也滿足了高損耗背板應用需求。而且,使用增強前向糾錯(FEC)等技術,能夠克服30 dB通道損耗,延長背板傳輸距離,支持使用低成本材料,而不會犧牲系統誤碼率(BER)。功能的增強提高了收發器的可用性。例如,硬核物理編碼子層(PCS)模塊可以處理8b/10b和64/66b等多種編碼方法,還為Interlaken和10 Gbps以太網(GbE)數據流提供關鍵的處理功能。而且,為PCI Express? (PCIe?) Gen1、Gen2和Gen3提供全面的協議棧。今后的FPGA將大規模采用串行存儲器。串行存儲器接口采用了10-15 Gbps高速串行收發器,克服并行存儲器接口的帶寬、延時和功耗局限。請參見圖4。

圖4.28 Gbps工作,采用了Altera的20 nm工藝技術

雖然某些應用需要最新的體系結構、IP和串行技術,例如,400G解決方案,但是,這對于其他應用不一定是最優方案,反而有可能影響其功耗和成本目標。有必要針對不同的FPGA和不同的應用而有選擇的使用這些技術。

處理器集成

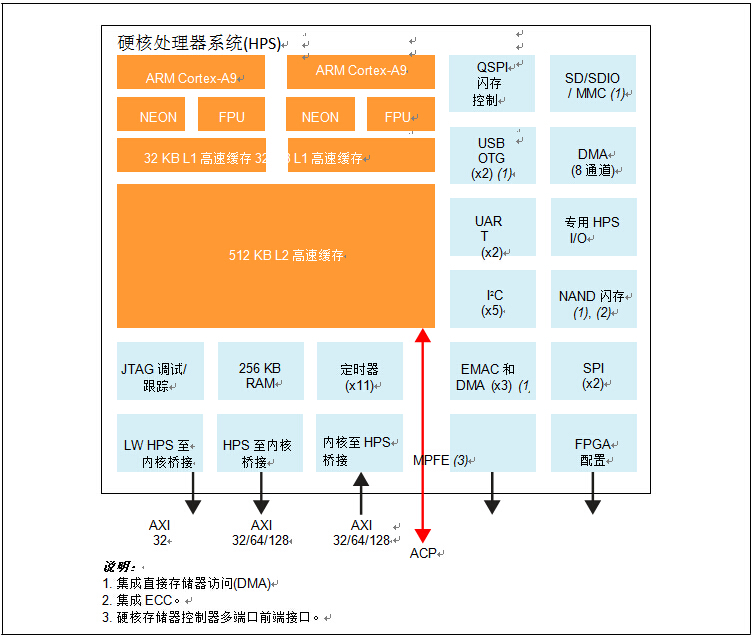

FPGA總是能夠提高電路板上組件的集成度,而影響最大的是最近集成了基于ARM的硬核處理器系統(HPS)。HPS集成了獨立但是高度集成的處理器以及硬核外設和可編程邏輯,開發了芯片系統(SoC)解決方案。這種集成是從28 nm可編程邏輯技術和ARM Cortex?-A9處理器開始的,FPGA中的這種體系結構得到了廣泛應用,這些SoC的發展將為ARM處理器供應商的長期產品發展路線產生積極影響。系統規劃人員現在有更多的選擇來提高集成度,增強系統性能、降低系統成本和功耗,減輕供應鏈風險。沒有采用這些可編程SoC的系統規劃人員會吃驚的發現:

■ 不同類型的器件系列有大量的SoC產品

■ 可編程邏輯和處理器之間的緊密集成提高了性能,降低了延時。

■ 工程師通過28 nm SoC、開發套件和工具來使用這一新技術

■ 部分FPGA供應商提供ARM輔助系統支持

圖5顯示采用了ARM Cortex-A9處理器的第二代HPS模塊。

圖5.采用了ARM Cortex-A9處理器的第二代HPS模塊

下一代FPGA和SoC即將出現

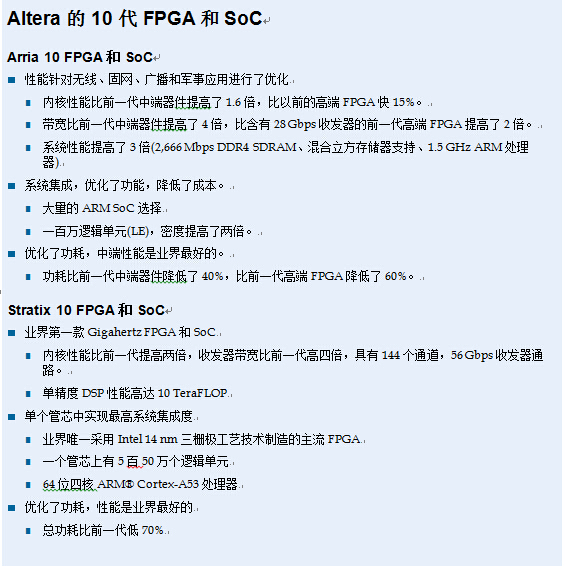

28 nm工藝節點之后發布下一代PLD的第一家公司是Altera,推出了10代系列產品。Altera使用了定制方法,所有PLD提供商在其各種低成本、中端和高端產品系列中廣泛使用了不同的工藝技術、不同的體系結構和IP以及不同的集成方法。第10代系列產品包括Stratix? 10以及Arria? 10 FPGA和SoC,滿足了需要一些中等速率收發器的應用需求,以及需要多個28和56 Gbps收發器的應用需求。通過在這兩種器件系列中采用定制方法,FPGA大幅度增強的功能是硬件規劃人員和系統設計人員還未預見到的。

硬件工程師使用目前一代Altera? FPGA,采用相同的高效能工具、IP和設計移植功能,充分發揮了這些FPGA的優勢。軟件開發人員已經能夠使用Altera的SoC開發套件和其他工具,針對ARM HPS進行設計。而且,設計工具流程的效能還會進一步增強。采用其他的設計工具和方法,例如開放計算語言(OpenCL?)等,支持采用C語言開發HDL,從而進一步縮短了設計開發時間。此外,Altera還認識到每年需要將編譯時間縮短兩倍才能跟上這些功能的快速發展。

結論

很多市場領域的系統規劃人員尋找ASIC和ASSP的替代方法,以及能夠滿足其帶寬、性能、集成度和功耗需求的解決方案。選擇好FPGA公司,其交付的產品在FPGA上具有前所未有的突破性優勢。為能夠滿足客戶在很多最終應用上的需求,還需要各種工具和選擇,例如,400G數據包處理、無線遠程射頻單元、數據中心和高性能計算等應用需求。使用了定制方法的產品策略針對不同的應用而采用不同的工藝技術、體系結構和集成選擇,為硬件規劃人員提供了最好的選擇和解決方案。Altera的10代系列產品定制了FPGA和SoC,在多種不同的應用中突破了功能,突出了產品優勢。

參考文獻

1. 思科視覺網絡指數(VNI):全球移動數據流量預測更新,2012 – 2017:www.cisco.com/en/US/solutions/collateral/ns341/ns525/ns537/ns705/ns827/ white_paper_c11-520862.html

2. 白皮書:采用28-nm FPGA設計多相DPD解決方案:www.altera.com/literature/wp/wp-01171-polyphase-dpd.pdf

3. Gartner報告,市場趨勢:全球,初次采用ASIC和ASSP的設計呈繼續下滑趨勢,2012

4. Altera網站:www.altera.com

5. Alter企業介紹

6. 福布斯網站:www.forbes.com/sites/greatspeculations/2013/01/22/intels-difficult-year-and- whats-ahead/

評論