Qsys與uC/OS學習筆記2:系統仿真

仿真在FPGA設計過程中舉足輕重,在板級調試前若不好好花功夫做一些前期的驗證和測試工作,后期肯定要不斷的返工甚至推倒重來,這是FPGA設計的迭代特性所決定的。因此,在設計的前期做足了仿真測試工作,雖然不能完全避免后期問題和錯誤的發生,卻能夠大大減少后期調試和排錯的工作量。

本文引用地址:http://www.104case.com/article/275553.htm邏輯設計中需要做仿真,是因為邏輯設計大都是設計者原型開發的,不做仿真的話設計者肯定心里也沒底。而用Qsys搭建的系統多是由已經成熟驗證過的IP核組成的,還需要仿真否?這是個仁者見仁智者見智的問題,特權同學也無意深入其中不能自拔。過去用SOPC Builder時還確實想動手做做這類帶CPU的系統級仿真,只可惜倒騰半天不是缺這個就是少那個,大都無功而返。這回上了Qsys,而且ModelSim-Altera對于Quatus II的支持也是做得越來越“體貼”了,所以今個再做了一些嘗試,果然成功了,原廠把工具的使用做得越來越傻瓜便利的同時,工程師們從中大大獲益。

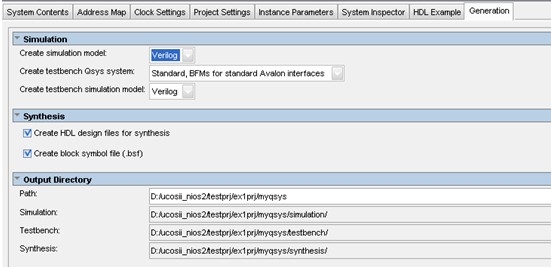

如圖1所示,首先在Generations的Simulation選項中做好設置。

圖1

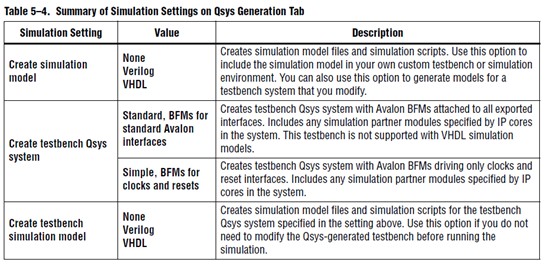

Simulation設置選項的具體含義如圖2所示。

圖2

因為都是用Verilog,所以simulation model和testbench simulation model我們都選擇Verilog,話說Altera其實主打的是Verilog語言,所以各種功能對Verilog的支持都是非常到位的,VHDL就不一定了。也用過Xilinx的東西,則正好相反。也不能談論孰優孰劣,也是習慣使然。

Standard和Simple的模型主要差別在于后者只是簡單的在testbench里產生clock和reset信號,而前者則會對所有export信號產生激勵或引出便于監視觀察。

確定完成Simulation的設置后就可以點擊左下角的Generate重新生成系統。

系統生成完畢,到“工程目錄myqsystestbenchmyqsys_tbsimulation”這個路徑下有測試腳本的頂層文件myqsys_tb.v,打開后代碼如下:

`timescale 1 ps / 1 ps

module myqsys_tb (

);

wire myqsys_inst_clk_bfm_clk_clk; // myqsys_inst_clk_bfm:clk -> [myqsys_inst:clk_clk, myqsys_inst_reset_bfm:clk]

wire myqsys_inst_reset_bfm_reset_reset; // myqsys_inst_reset_bfm:reset -> myqsys_inst:reset_reset_n

wire [7:0] myqsys_inst_led_pio_external_connection_export; // myqsys_inst:led_pio_external_connection_export -> myqsys_inst_led_pio_external_connection_bfm:sig_export

myqsys myqsys_inst (

.clk_clk (myqsys_inst_clk_bfm_clk_clk), // clk.clk

.reset_reset_n (myqsys_inst_reset_bfm_reset_reset), // reset.reset_n

.led_pio_external_connection_export (myqsys_inst_led_pio_external_connection_export) // led_pio_external_connection.export

);

altera_avalon_clock_source #(

.CLOCK_RATE (50)

) myqsys_inst_clk_bfm (

.clk (myqsys_inst_clk_bfm_clk_clk) // clk.clk

);

altera_avalon_reset_source #(

.ASSERT_HIGH_RESET (0),

.INITIAL_RESET_CYCLES (50)

) myqsys_inst_reset_bfm (

.reset (myqsys_inst_reset_bfm_reset_reset), // reset.reset_n

.clk (myqsys_inst_clk_bfm_clk_clk) // clk.clk

);

altera_conduit_bfm myqsys_inst_led_pio_external_connection_bfm (

.sig_export (myqsys_inst_led_pio_external_connection_export) // conduit.export

);

endmodule

該代碼中首先例化了被測試系統myqsys,將其3個export信號引出。然后分別針對這3個export信號產生相應的激勵和響應,即altera_avalon_clock_source用于產生clock,altera_avalon_reset_source用于產生reset信號,altera_conduit_bfm則用于觀察led_pio輸出。這三個模塊的詳細代碼都可以在同目錄的submodules子文件夾下找到。

接下來,我們需要打開EDS中的軟件工程并對其進行仿真。我們接著使用上一個筆記中創建的countbinary_prj工程進行仿真,首先我們需要到BSP Editor里面去重新generate,因為Qsys有改動并重新生成了。接著修改其main函數如下:

int main(void)

{

alt_u16 cnt;

for(cnt=0;cnt<256;cnt++)

{

IOWR_ALTERA_AVALON_PIO_DATA(LED_PIO_BASE,cnt);

}

while(1);

}

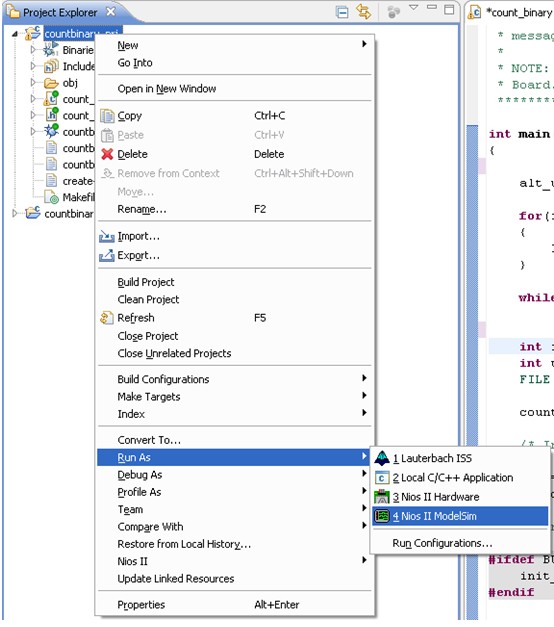

目前工程代碼執行的意圖是:在上電初始化完成后,led_pio會從0連續的遞增一直到255,然后停止。保存修改的軟件代碼并重新編譯工程,然后在應用工程上點擊右鍵值并選擇Rus asàNiso II ModelSim,如圖3所示。

圖3

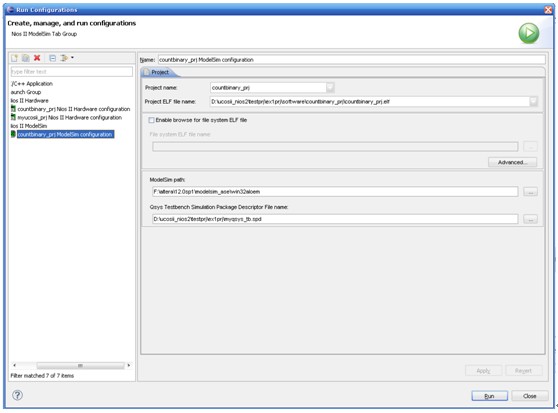

第一次運行通常會彈出如圖4所示的窗口,需要對仿真選項做一些配置。選擇選擇仿真的工程名(Project name)、仿真的elf可執行文件(Project ELF file name)、ModelSim軟件的安裝路徑(ModelSim path)和Qsys測試腳本封裝描述文件(Qsys Testbench Simulation Package Descriptor File name)存儲位置。設計好后點擊Run即啟動ModelSim進行仿真。

圖4

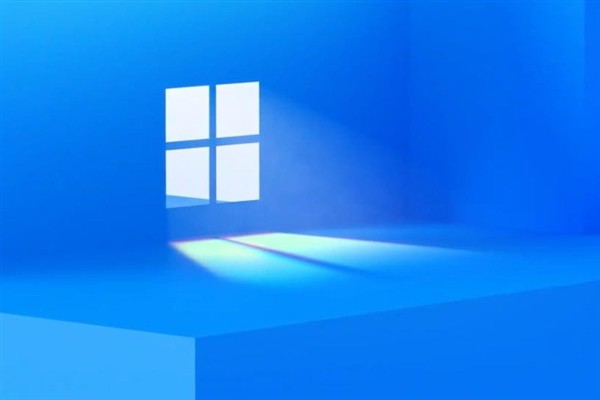

彈出ModelSim-Altera后,我們可以講頂層文件的3個export信號添加的Wave窗口中,然后Run起來,看看仿真時間有2-3秒后我們可以回放仿真波形(具體的時間需要看PC的狀況,特權同學的Pentium E5800跑了應該有半分多鐘),如圖5、圖6和圖7所示。

如圖5,剛上電0ns開始,reset信號有一段時間的低脈沖,大約50個clk周期,正如我們的testbench中所設計的。

圖5

如圖6所示,在仿真進行到大約1.3s時刻,led_pio信號有一段變化的波形,初始0值在經過這段變化波形后最終變為255,這也是我們軟件代碼里面所設置的最終值。

圖6

再來看圖7,我們將led_pio的變化段波形放大,果然是我們軟件編程的遞增的值,一直從0遞增到255為止。

圖7

仿真的流程基本就是這樣,很easy,我們只要動動指尖就可以完成,當然了,如果要做很多個性化的細致的仿真驗證,那么在testbench里面我們倒是可以動些手腳,輸出結果也不光只是看看波形而已。

評論