qsys 文章 最新資訊

Qsys與uC/OS學(xué)習(xí)筆記6:任務(wù)切換-續(xù)

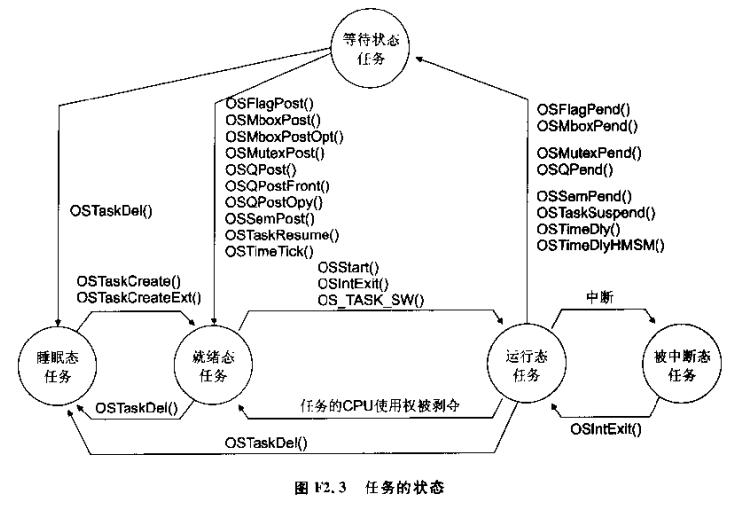

- uC/OS-II總是運行進(jìn)入就緒態(tài)任務(wù)中優(yōu)先級最高的任務(wù)。確定哪個優(yōu)先級最高,下面要由哪個任務(wù)運行了,這一工作是由任務(wù)調(diào)度函數(shù)OS_Sched (void)完成的。當(dāng)前就緒任務(wù)要交出CPU控制權(quán)并進(jìn)行任務(wù)切換的相關(guān)操作都調(diào)用了OS_Sched (void)函數(shù)。 如圖1所示,當(dāng)前運行態(tài)任務(wù)交出CPU控制權(quán)必須是以下某個函數(shù)被調(diào)用或某事件發(fā)生:OSFlagPend()、OSMboxPend()、OSMutexPend()、OSQPend()、OSSemPend()、OSTaskSuspend()、OS

- 關(guān)鍵字: Qsys uC/OS

Qsys與uC/OS-II學(xué)習(xí)筆記5:任務(wù)切換

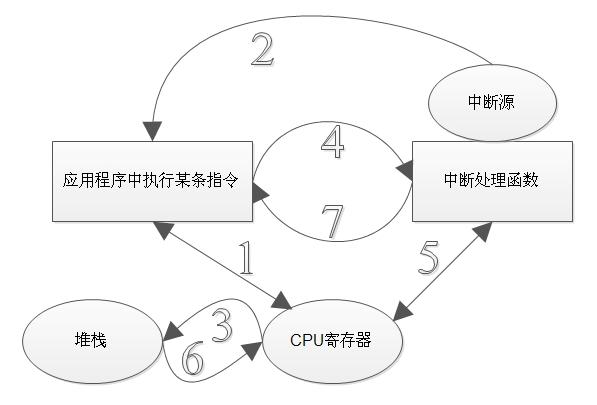

- 上個筆記提到調(diào)用任務(wù)延時函數(shù)后,系統(tǒng)將會進(jìn)行任務(wù)切換,否則當(dāng)前運行任務(wù)就會一直霸占著CPU的使用權(quán)。那么這個任務(wù)延時函數(shù)中到底有什么奧秘?調(diào)用它為什么能夠讓任務(wù)切換自如?這個筆記咱就要揭開uC/OS-II的一大設(shè)計精髓——任務(wù)切換。 特權(quán)同學(xué)并非軟件工程或是計算機(jī)科班出身,還真沒學(xué)過什么操作系統(tǒng),對于CPU內(nèi)部架構(gòu)和工作機(jī)制的理解和認(rèn)識完全靠自身的實踐、摸索加一些教科書的研讀。對于一些概念的闡述或許不夠?qū)I(yè),如果有些偏差也非常歡迎大家提出來加以糾正,但是我想這些“草根”式的圖文或許多少能夠幫助大家快

- 關(guān)鍵字: Qsys uC/OS-II

Qsys與uC/OS-II學(xué)習(xí)筆記4:任務(wù)狀態(tài)與工作機(jī)制

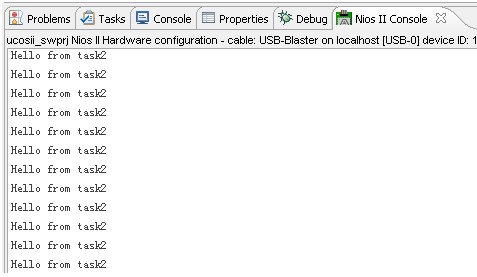

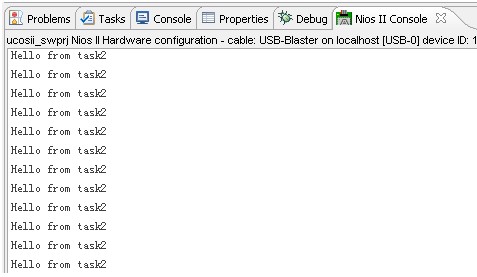

- 前面一個筆記我們已經(jīng)可以輕松的使用EDS提供的HAL構(gòu)建一個uC/OS-II的模板工程,在這個工程里,所有和移植有關(guān)的問題都不用我們操心,我們只要放心的去設(shè)計我們的應(yīng)用程序便可。而一個最簡單的uC/OS-II工程也已經(jīng)呈現(xiàn)在我們面前,三個最基本的步驟就可以完成一個我們曾經(jīng)以為多么神奇的操作系統(tǒng)。但是,雖然我們能夠構(gòu)建兩個最基本的任務(wù),但說實在話,我們還沒搞懂它到底如何工作的,依葫蘆畫瓢沒有錯,若能夠搞清楚它的工作機(jī)理就更好了。 先來回顧一下兩個task,如下代碼: /* Prints &q

- 關(guān)鍵字: Qsys uC/OS

Qsys與uCOS學(xué)習(xí)筆記3:Hello uC/OS-II

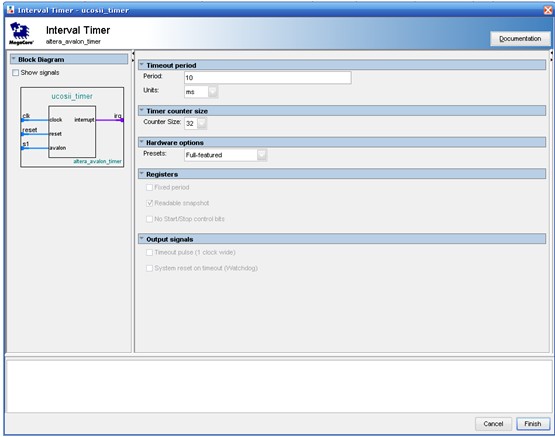

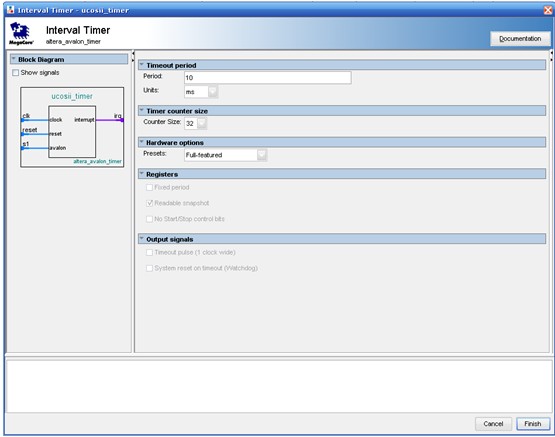

- uC/OS-II(又名Micro C/OS)是基于嵌入式系統(tǒng)的完整的,可移植、可固化、可裁剪的可剝奪型實時內(nèi)核,其已經(jīng)廣泛應(yīng)用在航空飛行器、醫(yī)療設(shè)備、工業(yè)控制等可靠性和穩(wěn)定性要求較高的場合。該內(nèi)核的代碼也是完全開源的,如果不做商業(yè)用途,完全免費。因此對于廣大的嵌入式愛好者與工程師們而言,了解OS從uC/OS-II開始不失為一個很好的選擇。 之前是使用特權(quán)同學(xué)自己的SF-NIOS2開發(fā)套件進(jìn)行了EDS上的uC/OS-II樣板工程測試,為了當(dāng)前學(xué)習(xí)筆記的持續(xù)性,這里重新就DE2-115板重新整理一個

- 關(guān)鍵字: Qsys uCOS

Qsys與uC/OS-II學(xué)習(xí)筆記4:任務(wù)狀態(tài)與工作機(jī)制

- 前面一個筆記我們已經(jīng)可以輕松的使用EDS提供的HAL構(gòu)建一個uC/OS-II的模板工程,在這個工程里,所有和移植有關(guān)的問題都不用我們操心,我們只要放心的去設(shè)計我們的應(yīng)用程序便可。而一個最簡單的uC/OS-II工程也已經(jīng)呈現(xiàn)在我們面前,三個最基本的步驟就可以完成一個我們曾經(jīng)以為多么神奇的操作系統(tǒng)。但是,雖然我們能夠構(gòu)建兩個最基本的任務(wù),但說實在話,我們還沒搞懂它到底如何工作的,依葫蘆畫瓢沒有錯,若能夠搞清楚它的工作機(jī)理就更好了。 先來回顧一下兩個task,如下代碼: /* Prints &q

- 關(guān)鍵字: Qsys uC/OS-II

Qsys與uCOS學(xué)習(xí)筆記3:Hello uC/OS-II

- uC/OS-II(又名Micro C/OS)是基于嵌入式系統(tǒng)的完整的,可移植、可固化、可裁剪的可剝奪型實時內(nèi)核,其已經(jīng)廣泛應(yīng)用在航空飛行器、醫(yī)療設(shè)備、工業(yè)控制等可靠性和穩(wěn)定性要求較高的場合。該內(nèi)核的代碼也是完全開源的,如果不做商業(yè)用途,完全免費。因此對于廣大的嵌入式愛好者與工程師們而言,了解OS從uC/OS-II開始不失為一個很好的選擇。 之前是使用特權(quán)同學(xué)自己的SF-NIOS2開發(fā)套件進(jìn)行了EDS上的uC/OS-II樣板工程測試,為了當(dāng)前學(xué)習(xí)筆記的持續(xù)性,這里重新就DE2-115板重新整理一個

- 關(guān)鍵字: Qsys uCOS

Qsys與uC/OS學(xué)習(xí)筆記2:系統(tǒng)仿真

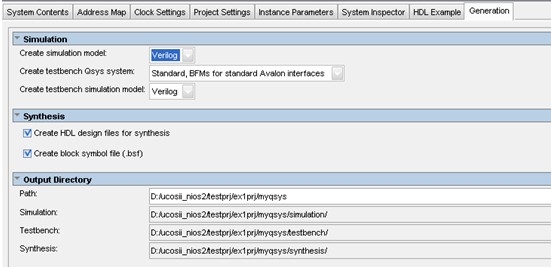

- 仿真在FPGA設(shè)計過程中舉足輕重,在板級調(diào)試前若不好好花功夫做一些前期的驗證和測試工作,后期肯定要不斷的返工甚至推倒重來,這是FPGA設(shè)計的迭代特性所決定的。因此,在設(shè)計的前期做足了仿真測試工作,雖然不能完全避免后期問題和錯誤的發(fā)生,卻能夠大大減少后期調(diào)試和排錯的工作量。 邏輯設(shè)計中需要做仿真,是因為邏輯設(shè)計大都是設(shè)計者原型開發(fā)的,不做仿真的話設(shè)計者肯定心里也沒底。而用Qsys搭建的系統(tǒng)多是由已經(jīng)成熟驗證過的IP核組成的,還需要仿真否?這是個仁者見仁智者見智的問題,特權(quán)同學(xué)也無意深入其中不能自拔

- 關(guān)鍵字: Qsys uC/OS

Qsys與uC/OS學(xué)習(xí)筆記1:與Qsys的第一次親密接觸

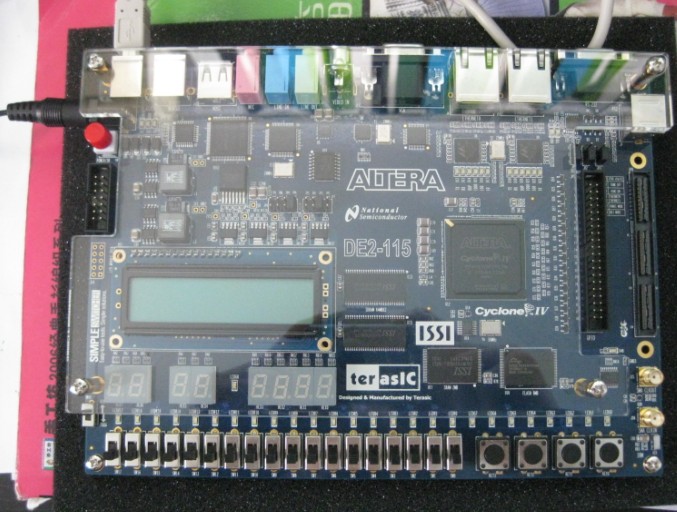

- 從Quartus II 11.0開始,喜新厭舊的Altera就不厭其煩的炒作SOPC Builder的替代者Qsys。記得去年參加他們的研討會時就已經(jīng)炒得火熱,如今12.0sp2都已經(jīng)release了,12以后更是完全摒棄了SOPC Buider,如果再不加緊找個理由上Qsys練練手,咱可就要OUT了。 正好近期對uC/OS非常感興趣,苦于手上沒有一款比較高端的板子用于實踐。于是通過層層關(guān)系最終在Altera的大學(xué)計劃經(jīng)理John處討得一套TerasIC的DE2-115,板載EP4CE115F2

- 關(guān)鍵字: Qsys uC/OS

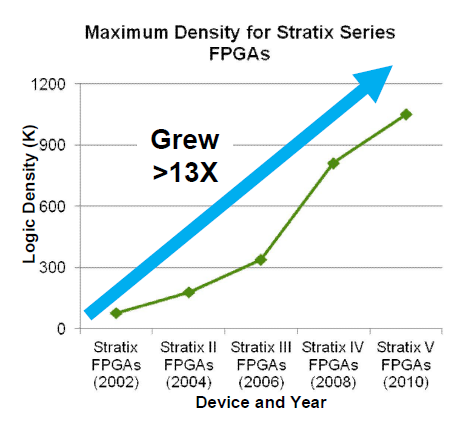

Altera全新Qsys工具加速FPGA產(chǎn)品上市步伐

- 在FPGA設(shè)計領(lǐng)域目前存在著三大主要難題:設(shè)計規(guī)模擴(kuò)大、設(shè)計重用、設(shè)計驗證時間太長。這三大難題嚴(yán)重影響著FPGA設(shè)計的效能,將減緩產(chǎn)品由研發(fā)到上市的時間,是亟需解決的重點問題。 2012年3月30日,“Altera亞太區(qū)采用Qsys實現(xiàn)系統(tǒng)集成研討會•北京站”在清華大學(xué)舉行,該活動重點介紹了Altera新的系統(tǒng)集成工具Qsys,及其如何通過Qsys提高設(shè)計效能。 簡化設(shè)計過程 隨著半導(dǎo)體技術(shù)的不斷發(fā)展,由于半導(dǎo)體工藝的不斷提升,器件的集成度也隨之提升

- 關(guān)鍵字: Altera FPGA Qsys

| 共10條 1/1 1 |

qsys介紹

您好,目前還沒有人創(chuàng)建詞條qsys!

歡迎您創(chuàng)建該詞條,闡述對qsys的理解,并與今后在此搜索qsys的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對qsys的理解,并與今后在此搜索qsys的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司