FPGA設(shè)計(jì)開(kāi)發(fā)軟件ISE使用技巧之:片上邏輯分析儀(ChipScope Pro)使用技巧

右邊一欄主要有兩個(gè)視窗:一個(gè)為“Trigger Setup”,用于設(shè)置觸發(fā)條件;一個(gè)為“Waveform”用于觀察波形。設(shè)置觸發(fā)條件包括設(shè)置觸發(fā)條件函數(shù)(Match)、觸發(fā)條件(Trig)和捕獲參數(shù)(Capture),下面分別介紹。

本文引用地址:http://www.104case.com/article/269338.htm(1)“Match”選項(xiàng)卡。

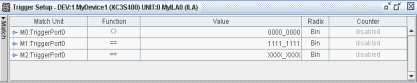

主要完成觸發(fā)條件函數(shù)的設(shè)置。所謂觸發(fā)條件函數(shù)是與表6.4中的匹配功能相對(duì)應(yīng)的。要設(shè)置數(shù)值大小和函數(shù),即選擇:=、<>、>、>=、<、<=某數(shù)值時(shí),才滿足觸發(fā)條件。當(dāng)有多個(gè)條件時(shí),可以分別設(shè)置每個(gè)條件的要求滿足的函數(shù)和數(shù)值,如圖6.53所示。

圖6.53 “Match”選項(xiàng)卡設(shè)置對(duì)話框

(2)“Trig”選項(xiàng)卡。

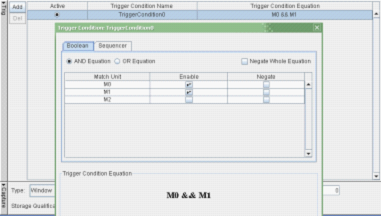

主要用于設(shè)置觸發(fā)條件。在“Match”下設(shè)置了觸發(fā)所需要滿足的條件。當(dāng)有多個(gè)條件時(shí)這里可以設(shè)置是讓哪一個(gè)條件起作用,也可以將條件設(shè)置為幾個(gè)條件的邏輯組合。或者是將幾個(gè)條件設(shè)置為“條件鏈”,即當(dāng)依次滿足條件鏈設(shè)置的各個(gè)條件后,才可以捕獲數(shù)據(jù),如圖6.54所示。

圖6.54 “Trig”選項(xiàng)卡設(shè)置對(duì)話框

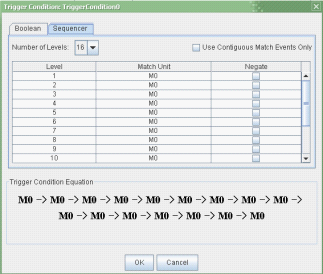

如圖6.54所示,單擊“Trigger Condition Equation”下的選項(xiàng),會(huì)彈出如圖6.55所示的對(duì)話框。在對(duì)話框中,有兩個(gè)選項(xiàng)卡。在“Boolean”選項(xiàng)卡下,可以設(shè)置哪一個(gè)條件起作用,也可將條件設(shè)置為幾個(gè)條件的邏輯組合;在“Sequencer”選項(xiàng)卡下,可以設(shè)置條件鏈,如圖6.55所示。當(dāng)依次滿足條件鏈下的幾個(gè)條件后,就被觸發(fā)。

圖6.55 “Sequencer”選項(xiàng)卡設(shè)置對(duì)話框

4.觀測(cè)波形

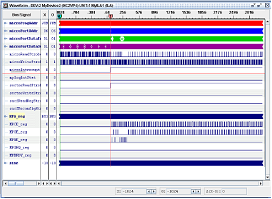

觸發(fā)條件設(shè)置好后,單擊左上角的![]() 按鈕開(kāi)始執(zhí)行。當(dāng)滿足觸發(fā)條后,ChipScope Pro開(kāi)始采集數(shù)據(jù),采集到一定數(shù)目后(該數(shù)目取決于存儲(chǔ)深度),就可以觀察波形了。如圖6.56為ChipScope Pro顯示波形的效果圖。

按鈕開(kāi)始執(zhí)行。當(dāng)滿足觸發(fā)條后,ChipScope Pro開(kāi)始采集數(shù)據(jù),采集到一定數(shù)目后(該數(shù)目取決于存儲(chǔ)深度),就可以觀察波形了。如圖6.56為ChipScope Pro顯示波形的效果圖。

在波形顯示窗口下可對(duì)波形進(jìn)行放大![]() 和縮小

和縮小![]() ,也可以進(jìn)行局部放縮

,也可以進(jìn)行局部放縮![]() 。當(dāng)要觀察總

。當(dāng)要觀察總

圖6.56 ChipScope Pro波形顯示效果圖

線數(shù)據(jù)時(shí),可以先選中所有總線數(shù)據(jù),然后單擊右鍵,選擇“Add to Bus”/“New Bus”即可,如圖6.57所示。

圖6.57 組合總線數(shù)據(jù)

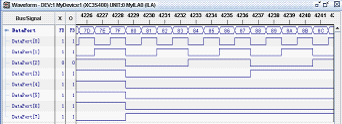

添加成功后,就可以在新生成的bus下看到總線數(shù)據(jù)。如圖6.58所示,圖中DataPort為新生成的總線,設(shè)計(jì)者可以根據(jù)需要修改總線的名稱。

圖6.58 總線數(shù)據(jù)生成結(jié)果

6.7.5 小結(jié)

本節(jié)對(duì)在線邏輯分析工具ChipScope Pro作了詳細(xì)介紹。通過(guò)本節(jié)的學(xué)習(xí),讀者應(yīng)該掌握ChipScope Pro的設(shè)計(jì)流程以及使用方法。

ChipScope Pro本身的功能很強(qiáng)大,在調(diào)試階段應(yīng)用很廣泛。它可以觀察FPGA內(nèi)部的任何信號(hào),使用也比較簡(jiǎn)單,希望讀者能夠很好地掌握。

為了讓讀者能夠盡快地熟悉這一工具的使用,在6.8節(jié)給出一個(gè)簡(jiǎn)單的實(shí)例,分別應(yīng)用兩種設(shè)計(jì)流程來(lái)完成,讀者可參照這一例程來(lái)進(jìn)一步熟悉ChipScope Pro的使用。

fpga相關(guān)文章:fpga是什么

評(píng)論