FPGA設(shè)計開發(fā)軟件ISE使用技巧之:片上邏輯分析儀(ChipScope Pro)使用技巧

6.7.3 ChipScope Pro Core Inserter簡介

本文引用地址:http://www.104case.com/article/269338.htmChipScope Pro Core Inserter的啟動有兩種方式。

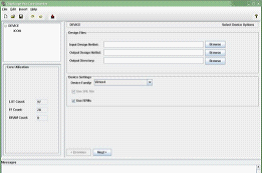

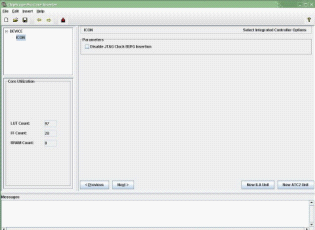

(1)直接在Windows環(huán)境下運行“開始”/“程序”/“ChipScope Pro 8.2i”/“ChipScope Pro Core Inserter”命令。運行后即可得到ChipScope Pro Core Inserter的用戶界面,如圖6.36所示。

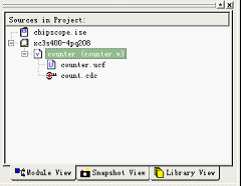

(2)可以通過新建資源的方法,如圖6.37所示。

新建ChipScope Pro Inserter資源后,系統(tǒng)自動生成擴展名為cdc的文件。如圖6.38所示,雙擊擴展名為cdc的文件即可啟動ChipScope Pro Inserter界面。需要注意的是,在雙擊擴展名為cdc的文件時,系統(tǒng)會先對該工程文件進(jìn)行綜合。綜合完成后才會啟動ChipScope Pro Inserter。

圖6.36 ChipScope Pro Core Inserter用戶界面

圖6.37 新建ChipScope Pro Inserter資源對話框 圖6.38 新建ChipScope Pro Core Inserter資源后的界面

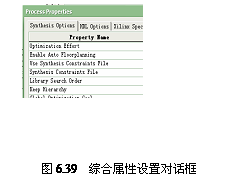

這里在綜合前必須先對綜合屬性進(jìn)行設(shè)置,如圖6.39所示,在綜合屬性對話框中對“synthesis options”/“keep Hierarchy”選項進(jìn)行設(shè)置。設(shè)置“keep Hierarchy”為“Yes”或“Soft”。

雙擊擴展名為cdc的文件,系統(tǒng)完成綜合后,會自動啟動ChipScope Pro Core Inserter。設(shè)計者通過ChipScope Pro Core Inserter對觸發(fā)單元個數(shù)、觸發(fā)寬度、觸發(fā)條件、存儲深度、采樣時刻等參數(shù)進(jìn)行設(shè)置。設(shè)置完畢后,在ISE下完成布局布線,下載配制文件,即可用ChipScope Pro Analyzer進(jìn)行觀測。

下面對ChipScope Pro Core Inserter的各項設(shè)置做詳細(xì)的說明。

1.用戶界面

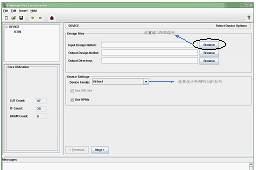

啟動ChipScope Pro Core Inserter后,顯示如圖6.40所示的界面。在“Input Design Netlist”文本框中設(shè)置輸入設(shè)計網(wǎng)表的路徑。設(shè)置好后,“Output Design Netlist”和“Output Directory”會自動生成,設(shè)計者也可自己指定。

圖6.40 ChipScope Pro Core Inserter用戶界面

如果是通過新建資源的方法啟動ChipScope Pro Core Inserter,這幾項顯示為灰色,無需設(shè)計者設(shè)置,系統(tǒng)會自動找到設(shè)計網(wǎng)表文件。在“Device Family”下拉列表中選取設(shè)計所用的FPGA后,就可單擊“Next”按扭,進(jìn)入“Select Integrated Controller Options”對話框,如圖6.41所示。

圖6.41 “Select Integrated Controller Options”對話框

2.“Select Integrated Controller Options”對話框設(shè)置

在如圖6.40所示的“Select Device Options”對話框中,可以指定是否禁止在JTAG時鐘上插入BUFG。如果選中此項,JTAG時鐘將使用普通布線資源,而不是全局時鐘布線。這樣會在JTAG時鐘線上產(chǎn)生較大的布線延時。因此在全局時鐘資源足夠用的情況下,應(yīng)該盡量使JTAG時鐘使用BUFG資源。即使由于全局時鐘資源不夠而不得不禁用BUFG時,也最好附加相應(yīng)約束,使延遲抖動盡量小。推薦設(shè)計者在使用時不選此項。

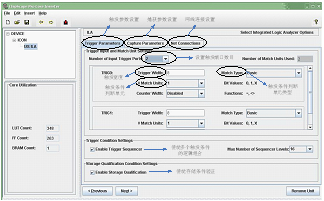

單擊“Next”按鈕,進(jìn)入“Select Integrated Logic Analyzer Options”對話框,如圖6.42所示。

圖6.42 “Select Integrated Logic Analyzer Options”ILA對話框

3.“Select Integrated Logic Analyzer Options”對話框設(shè)置

如圖6.42所示,可以看到在“Select Integrated Logic Analyzer Options”ILA對話框下有3個選項卡,可對觸發(fā)參數(shù)、捕獲參數(shù)、網(wǎng)線連接進(jìn)行設(shè)置。

“Trigger Parameters”選項卡可對觸發(fā)端口數(shù)目,每個觸發(fā)端口的寬度、觸發(fā)條件判斷單元、觸發(fā)條件判斷單元的個數(shù)和類型等進(jìn)行設(shè)置。

(1)觸發(fā)端口數(shù)目。

在設(shè)計中可以根據(jù)需要設(shè)置多個觸發(fā)端口,每個ILA Core最多可以有16個輸入觸發(fā)端口,每個觸發(fā)端口下又可設(shè)置多個觸發(fā)條件判斷單元,但各個觸發(fā)端口包含的觸發(fā)條件判斷單元數(shù)量之和不能大于16。

(2)觸發(fā)端口設(shè)置。

一個完整的觸發(fā)端口設(shè)置包括:觸發(fā)寬度、觸發(fā)條件判斷單元個數(shù)及類型的設(shè)置。觸發(fā)寬度是指觸發(fā)端口包含信號線的個數(shù)。通過觸發(fā)條件判斷單元進(jìn)行判斷,當(dāng)信號線上的信號滿足設(shè)定的條件時,ChipScope Pro就可將其捕獲并存儲在BlockRam中,用于在ChipScope Pro Analyzer中顯示波形。

對觸發(fā)條件可以設(shè)置個數(shù)和類型。當(dāng)有多個觸發(fā)條件時,可以將觸發(fā)條件設(shè)置為幾個觸發(fā)條件的邏輯組合。觸發(fā)條件判斷單元實際為比較器,其類型可以有以下幾種,如表6.4所示。

fpga相關(guān)文章:fpga是什么

評論