FPGA設(shè)計開發(fā)軟件ISE使用技巧之:編譯與仿真設(shè)計工程

6.5 編譯與仿真設(shè)計工程

本文引用地址:http://www.104case.com/article/269336.htm編寫代碼完成之后,一個很重要的工作就是驗(yàn)證代碼功能的正確性,這就需要對代碼進(jìn)行編譯與仿真。編譯主要是為了檢查代碼是否存在語法錯誤,仿真主要為了驗(yàn)證代碼實(shí)現(xiàn)的功能是否正確。

編譯和仿真設(shè)計工程在整個設(shè)計中占有很重要的地位。因?yàn)榇a功能不正確或代碼的編寫風(fēng)格不好對后期的設(shè)計會有很大的影響,所以需要花很多時間在設(shè)計工程的仿真上。

在這一節(jié)中將通過一個具體的實(shí)例來介紹如何對編譯工程代碼以及如何使用ISE自帶的仿真工具ISE Simulator進(jìn)行仿真。

1.編譯工程代碼

編譯主要是為了檢測代碼是否存在語法錯誤。在ISE下,源代碼的編寫是在HDL Editor下完成的,但在HDL Editor下沒有專門用于編譯代碼的選項(xiàng)。不過在HDL Editor下完成代碼的編寫后,單擊“保存”按鈕,HDL Editor就會自動對代碼進(jìn)行編譯。如果代碼存在語法錯誤,就會在信息顯示窗中顯示出來,用戶可以根據(jù)顯示的提示,查找語法錯誤并修改。

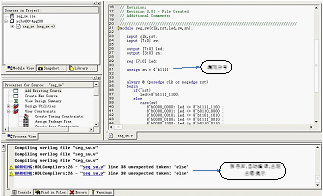

如圖6.17所示為在輸寫代碼時忘記分號,保存后就會有提示信息。

當(dāng)不存在錯誤時,提示信息就不會出現(xiàn)“Warning”。ISE下對于代碼的編譯功能并不是很強(qiáng)大,有很多錯誤是檢測不出來的。例如在編寫Verilog代碼時,寫case語句時漏寫了end case語句,在HDL Editor下是檢查不出來的。但這些錯誤在仿真或綜合階段是可以檢測出來的,因此即使完成了編譯沒有錯誤,也一定要進(jìn)行仿真,檢查是否還存在其他的錯誤。

2.仿真設(shè)計工程

這里以一個具體的實(shí)例來介紹ISE下自帶的仿真工具ISE Simulator的使用,代碼參見本書實(shí)例代碼。該例程的主要功能是根據(jù)撥碼開關(guān)(sw)輸入的值在數(shù)碼管(seg_led)上顯示相應(yīng)的數(shù)值。

圖6.17 編譯后的出錯提示

ISE Simulator的使用主要是借助于ISE的輔助設(shè)計工具HDL Bencher(測試激勵生成器)來完成的。用戶將VHDL源代碼、Verilog源代碼或ECS原理圖等設(shè)計輸入導(dǎo)入工程后,用戶可以在圖形界面下編輯測試波形,HDL Bencher可以根據(jù)用戶編輯的測試波形自動生成測試激勵文件,然后調(diào)用ISE中的ISE Simulator進(jìn)行仿真。可見使用ISE Simulator進(jìn)行仿真主要分兩步。

(1)調(diào)用HDL Bencher,編輯測試波形,生成測試激勵文件。

(2)調(diào)用ISE Simulator對工程文件進(jìn)行功能仿真和時序仿真。

下面對實(shí)例做詳細(xì)的介紹,具體步驟如下。

(1)啟動HDL Bencher。

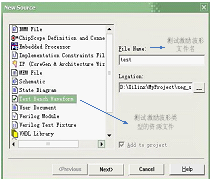

首先打開實(shí)例工程,選擇“Project”/“New Source”,彈出新建資源的對話框,選擇“Test Bench Waveform”,輸入測試激勵波形文件名,如圖6.18所示。

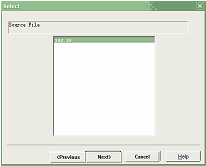

單擊“下一步”按鈕為測試激勵文件選擇源文件,如圖6.19所示,選擇要測試的源代碼,單擊“下一步”按鈕。

圖6.18 新建測試測試激勵波形文件 圖6.19 為被測試的源文件對話框

單擊“完成”按鈕確認(rèn)新建資源信息,HDL Bencher會自動啟動。

(2)波形編輯。

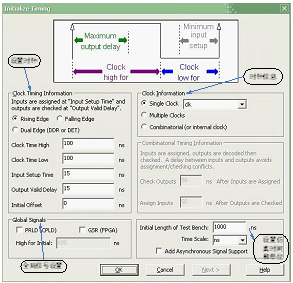

HDL Bencher啟動后首先出現(xiàn)如圖6.20所示的時鐘設(shè)置對話框。

圖6.20 時鐘設(shè)置對話框

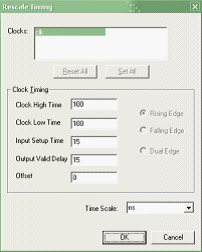

如圖6.20所示,時鐘設(shè)置包括:時鐘的高電平持續(xù)時間(Clock Time High)、低電平持續(xù)時間(Clock Time Low)、建立時間(Input Setup Time)和保持時間(Output Valid Delay),系統(tǒng)為單時鐘(Single Clock)系統(tǒng)、多時鐘(Multiple Clocks)系統(tǒng)以及仿真時間和單位。這里設(shè)置的仿真時間表示仿真將持續(xù)多長時間后自動停止。

如果設(shè)計存在異步時序(Asynchronous Signal Support),還要對異步時鐘做相應(yīng)的設(shè)置。這個設(shè)計中,只有同步時序,所以不選,與上表設(shè)置不一致之處請用戶自行修改。設(shè)置完畢單擊“OK”按鈕后系統(tǒng)會自動生成時鐘的波形,如圖6.21所示。

圖6.21 波形編輯界面

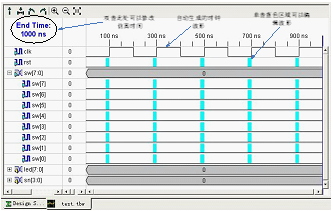

如圖6.21所示,設(shè)置好時鐘后,系統(tǒng)會自動生成時鐘波形。在如圖6.18所示的對話框中設(shè)置的“Initial Length of Test Bench”為1000ns,這里可以看到仿真在進(jìn)行了1000ns后就自動停止了,雙擊“End Time”,會彈出如圖6.22所示的對話框,可以對仿真時間進(jìn)行修改。

在設(shè)置好時鐘頻率、時鐘建立時間和保持時間后,如果要修改,選擇“Test Bench”/“Rescale Timing”會彈出如圖6.23所示對話框,可以對時鐘設(shè)置進(jìn)行修改。

圖6.22 修改仿真時間對話框 圖6.23 修改時鐘設(shè)置對話框

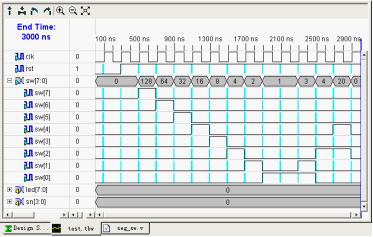

這此設(shè)計中除時鐘信號外,rst和sw[7:0]為輸入信號,需要對rst和sw的波形進(jìn)行編輯,編輯方法也比較簡單,單擊圖中的藍(lán)色區(qū)域就可以改變波形,根據(jù)仿真需要可任意設(shè)置波形,在這里設(shè)置仿真波形如圖6.24所示。

圖6.24 編輯波形圖

fpga相關(guān)文章:fpga是什么

評論