基于FPGA的彩色TFT-LCD控制電路設計及其ASIC實現

3.2 有限狀態機模塊

本文引用地址:http://www.104case.com/article/266853.htm有限狀態機由兩個16位的行列計數器組成,狀態變量為模式寄存器的狀態/復位位。在工作模式下,兩個計數器循環計數。當行計數器狀態與起始行寄存器相同時,行有效信號變高,表示該幀圖像的顯示開始,此時數據處理器模塊開始工作。在系統復位或行計數器狀態與終止行寄存器相同時,行計數器被復位。在行有效信號變高后,當列計數器狀態與起始列寄存器相同時,像素有效信號變高,表示該行的有效顯示開始,此時數據處理器開始輸出每個像素的顏色數據。在系統復位或列計數器狀態與終止列寄存器相同時,列計數器被復位。

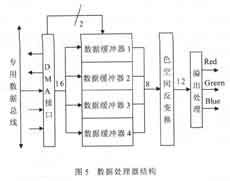

3.3 數據處理器模塊

數據處理器模塊如圖5所示。它由三部分組成:DMA接口及其數據緩沖器、色空間反變換電路和溢出處理電路。根據系統設計要求,由電荷耦合器件(CCD)圖像傳感器采樣得到的原始圖像經過像素處理器模塊的內插和色空間變換后,成為了YCbCr格式的圖像,根據JPEG標準,從RGB到 YCbCr的色空間變換遵循公式[3]

Y=0299R+0587G+0.114B

Cb=_0.169R-0.331G+0.5B (1)

Cr=0.5R-0.4186F-0.0814B

同時為了存儲方便,將變換得到的Y信號減去了128,這樣三種信號的值均在-128到+127之間,從而都可以用8位的帶符號數表示。在存儲YCbCr 信號時像素處理器模塊將相鄰像素的色度信號取均值然后進行復用,這樣節省了存儲空間。所以在圖像存儲器中相鄰兩個像素的亮度信號組合成一個16位的數據存放在一個存儲單元里,而復用的色度信號則存放在下一個地址的單元里[3] 。當要用液晶顯示器進行圖像顯示時,先通過連續兩次DMA的讀操作獲得兩個像素的亮度信號和色度信號,分別放入16位的數據緩沖器1和2,然后在讀取新的兩個相鄰像素的YCbCr信號并把它們放入數據緩沖器3和4的同時開始處理緩沖器1和2中的數據,于是通過兩對數據緩沖器的作用實現了一個簡單的流水線操作。在色空間反變換中要實現將YCbCr信號轉換成液晶顯示所需要的RGB信號,根據公式(1)并進行簡化我們可以得到相應的反變換的公式(2)。

(2)

(2)

根據反變換系數的范圍,我們將所有的系數值乘上64,然后將乘積的整數部分用一個8位的帶符號數表示。在色空間反變換中我們設計了一個9× 8的Booth乘法器,用來實現色度信號和變換系數的帶符號乘法運算。為了保證反變換的正確,在運算過程中要進行符號擴展,所以變換所得的RGB信號是12位的帶符號數,而最終輸出到數模轉換器的數據是8位無符號數,因此還要進行溢出處理,將所有的計算結果都限定在0~255范圍內。同時由于液晶顯示器的公共電極的電位是交流電位,即相鄰兩行的公共電極的電位是反相的,所以相鄰兩行的圖像數據應該分別以原碼和反碼輸出。

3.4 脈沖發生器模塊

脈沖發生器根據有限狀態機中行列計數器的狀態和波形參數寄存器內的參數,產生各驅動波形,這些驅動波形用于驅動液晶顯示模塊本身及其外接的模擬前端電路。

4 Verilog語言實現和FPGA硬件驗證

在確定了整體以及各功能模塊的結構設計之后,就可以用Verilog HDL語言對設計進行RTL建模,然后用Synopsys 公司的VCS對設計進行仿真并調試。通過RTL級的仿真后,我們對此電路進行了FPGA的硬件驗證,使用的芯片是Xilinx公司的VirtexE1000-BG560,系統時鐘為54MHz。無論是單獨測試還是作為整個數碼相機專用芯片的一部分,液晶顯示控制電路都能成功實現兩種工作模式下的設計要求,性能良好。

5結束語

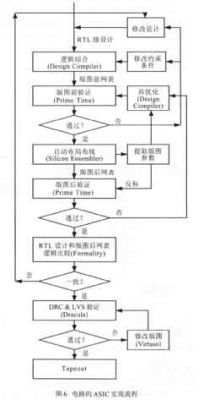

通過FPGA驗證后,液晶顯示控制電路用TSMC 0.25mm SAGETM工藝實現,后端流程如圖6所示,其中的Design Compiler,Prime Time和Formality是Synopsys公司的產品;Silicon Ensembler和Virtuso是Cadence公司的產品。圖像采樣接口的電路規模為15000門左右,芯片面積為0.49mm×0.8mm。

LCD顯示屏相關文章:lcd顯示屏原理

fpga相關文章:fpga是什么

led顯示器相關文章:led顯示器原理

lcd相關文章:lcd原理 脈沖點火器相關文章:脈沖點火器原理

評論