基于DSP Builder的VGA接口系統(tǒng)設(shè)計

VGA顯像原理

本文引用地址:http://www.104case.com/article/257524.htm顯示器通過光柵掃描的方式,電子束在顯示屏幕上有規(guī)律地從左到右、從上到下掃描。在掃描過程中,受行同步信號控制,逐點往右掃,完成一行掃描的時間倒數(shù)為行頻;同時又在行同步脈沖期內(nèi)回到屏幕的左端,從上往下形成一幀,在垂直方向上受場同步信號控制,完成一幀的時間倒數(shù)為場頻。圖像的顯示過程即為在電子束掃描過程中,將地址與圖像的像素依次對應(yīng),每一個被尋址的像素只獲得其自身的控制信息,而與周圍的像素不發(fā)生干擾,從而可以顯示穩(wěn)定的圖像。

VGA接口是顯示卡上輸出模擬信號的接口,也叫D-Sub接口。這種接口上面共有15個針孔,分成3排,每排5個,通過模擬VGA接口顯示圖像的工作原理,將計算機內(nèi)部以數(shù)字方式生成的顯示圖像信息,通過顯卡中的ADC轉(zhuǎn)變?yōu)镽、G、B三基色信號和行、場同步信號,通過電纜傳輸?shù)斤@示設(shè)備中。

VGA時序

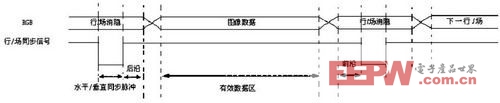

VGA的時序包括水平時序和垂直時序,且兩者都包含的時序參數(shù)有:水平(垂直)同步脈沖、水平(垂直)同步脈沖結(jié)束到有效顯示數(shù)據(jù)區(qū)開始之間的寬度(后沿)、有效顯示區(qū)寬度、有效數(shù)據(jù)顯示區(qū)結(jié)束到水平(垂直)同步脈沖寬度開始之間的寬度(前沿)。水平有效顯示區(qū)寬度與垂直有效顯示區(qū)寬度邏輯與的區(qū)域為可視區(qū)域,其他區(qū)域為消隱區(qū)。

一行或一場的時序信息如圖1所示。

圖1行/場時序圖

根據(jù)目前的顯示器性能參數(shù),以LG505E為例,其最大分辨率已可達到@60Hz">1024×768@60Hz,水平掃描頻率30kHz54kHz,垂直掃描頻率50Hz120Hz,帶寬75MHz。

基于DSPBuilder的VGA接口設(shè)計方法

本設(shè)計需要完成的功能包括產(chǎn)生VGA時序以及基于VGA接口的信號顯示。設(shè)計符合VGA接口標準的接口系統(tǒng),在該系統(tǒng)下可顯示一維矢量信號與二維圖像信號,并體現(xiàn)系統(tǒng)的可集成性,將該接口集成到SOPC系統(tǒng)中。

系統(tǒng)時鐘確定

根據(jù)系統(tǒng)時鐘計算公式:

時鐘頻率=(行像素數(shù)+行消隱點數(shù))×(一場行數(shù)+消隱行數(shù))×刷新率。

對于標準的VGA接口時序@60Hz">640×480@60Hz而言,時鐘頻率為800×525×60=25.175MHz。

在本設(shè)計中我們采用@60Hz">1024×768@60Hz的XGA顯示方式,因此系統(tǒng)的時鐘頻率PixelClk=1344×806×60=64.99MHz。

評論