LED 芯片封裝缺陷檢測方法及機理研究

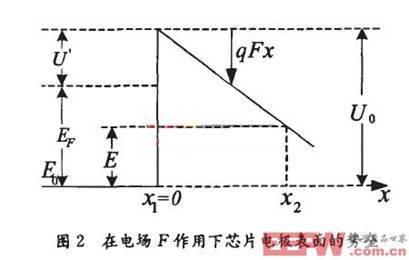

圖2為在電場f’作用‘F芯片電極表面的勢壘圖,其中EF為費米能級,U'為電子發(fā)射勢壘。由圖2

若芯片電極表面為突變結(jié),其值為U0,光生電流在隧道結(jié)兩側(cè)形成的電場強度為F,電極表面以外的勢壘為U0- qFx。取芯片電極導(dǎo)帶底為參考能級E0(x=0),因而有x0處,U(x)=0;x>0處,U(x)=U0- qFx,根據(jù)條件U(x)=E=U0- qFx2

式中d為膜層厚度,V為膜層隧道結(jié)兩側(cè)電壓。當(dāng)LED芯片發(fā)生光生伏特效應(yīng)時,由式(7)可知,流過芯片電極表面非金屬膜層的電流受到膜層厚度的影響,隨著膜層增厚,流過膜層的電流減小,流過LED支架回路的光電流也將減小。

綜上所述,引腳式LED支架回路光電流的有無或大小可以反映封裝工藝中LED芯片的功能狀態(tài)及芯片電極與引線支架的電氣連接情況,因此,可以通過檢測LED支架回路光電流達到檢測引腳式封裝工藝中芯片功能狀態(tài)和封裝缺陷。

評論