LED 芯片封裝缺陷檢測方法及機(jī)理研究

LED(Light-emitting diode)由于壽命長、能耗低等優(yōu)點(diǎn)被廣泛地應(yīng)用于指示、顯示等領(lǐng)域。可靠性、穩(wěn)定性及高出光率是LED取代現(xiàn)有照明光源必須考慮的因素。封裝工藝是影響LED功能作用的主要因素之一,封裝工藝關(guān)鍵工序有裝架、壓焊、封裝。由于封裝工藝本身的原因,導(dǎo)致LED封裝過程中存在諸多缺陷(如重復(fù)焊接、芯片電極氧化等),統(tǒng)計(jì)數(shù)據(jù)顯示[1。2]:焊接系統(tǒng)的失效占整個(gè)半導(dǎo)體失效模式的比例是25%~30%,在國內(nèi)[33,由于受到設(shè)備和產(chǎn)量的雙重限制,多數(shù)生產(chǎn)廠家采用人工焊接的方法,焊接系統(tǒng)不合格占不合格總數(shù)的40%以上。從使用角度分析,LED封裝過程中產(chǎn)生的缺陷,雖然使用初期并不影響其光電性能,但在以后的使用過程中會(huì)逐漸暴露出來并導(dǎo)致器件失效。在LED的某些應(yīng)用領(lǐng)域,如高精密航天器材,其潛在的缺陷比那些立即出現(xiàn)致命性失效的缺陷危害更大。因此,如何在封裝過程中實(shí)現(xiàn)對LED芯片的檢測、阻斷存在缺陷的LED進(jìn)入后序封裝工序,從而降低生產(chǎn)成本、提高產(chǎn)品的質(zhì)量、避免使用存在缺陷的LED造成重大損失就成為LED封裝行業(yè)急需解決的難題。

目前,LED產(chǎn)業(yè)的檢測技術(shù)主要集中于封裝前晶片級的檢測[“]及封裝完成后的成品級檢測睜7I,而國內(nèi)針對封裝過程中LED的檢測技術(shù)尚不成熟。本文在LED芯片非接觸檢測方法的基礎(chǔ)上睜9J,在LED引腳式封裝過程中,利用p-n結(jié)光生伏特效應(yīng),分析了封裝缺陷對光照射LED芯片在引線支架中產(chǎn)生的回路光電流的影響,采用電磁感應(yīng)定律測量該回路光電流,實(shí)現(xiàn)LED封裝過程中芯片質(zhì)量及封裝缺陷的檢測。

1理論分析

1.1 p-n結(jié)的光生伏特效應(yīng)[m]根據(jù)p-n結(jié)光生伏特效應(yīng),光生電流IL表示為:

式中,A為p-n結(jié)面積,q是電子電量,Ln、Lp分別為電子和空穴的擴(kuò)散長度,J表示以光子數(shù)計(jì)算的平均光強(qiáng),α為p-n結(jié)材料的吸收系數(shù),β是量子產(chǎn)額,即每吸收一個(gè)光子產(chǎn)生的電子一空穴對數(shù)。

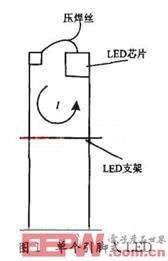

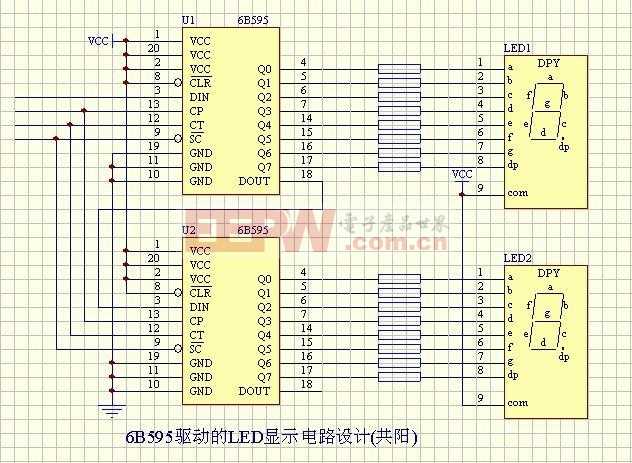

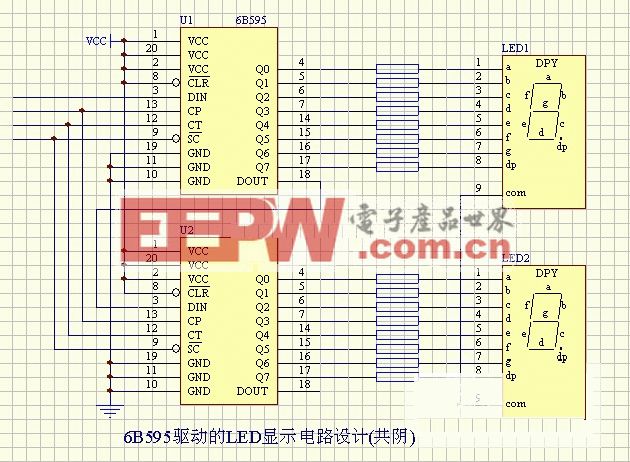

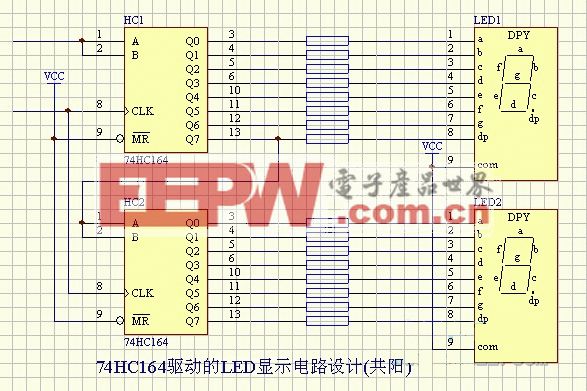

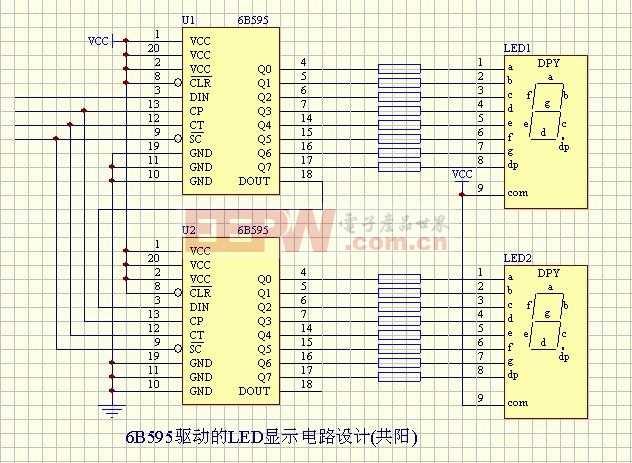

在LED引腳式封裝過程中,每個(gè)LED芯片是被固定在引線支架上的,LED芯片通過壓焊金絲(鋁絲)與引線支架形成了閉合回路,如圖1。若忽略引線支架電阻,LED支架回路光電流等于芯片光生電流IL。可見,當(dāng)p-n結(jié)材料和摻雜濃度一定時(shí),支架回路光電流與光照強(qiáng)度I成正比。

1.2封裝缺陷機(jī)理

LED芯片受到腐蝕因素影響或沾染油污時(shí),在芯片電極表面生成一層非金屬膜,產(chǎn)生封裝缺陷[11]。電極表面存在非金屬膜層的LED芯片壓焊工序后,焊接處形成金屬一介質(zhì)-金屬結(jié)構(gòu),也稱為隧道結(jié)。當(dāng)一定強(qiáng)度的光照射在LED芯片上,若LED芯片失效,支架回路無光電流流過若非金屬膜層足夠厚,只有極少數(shù)電子可以隧穿膜層勢壘,LED支架回路也無光電流流過;若非金屬膜層較薄,由于LED芯片光生電流在隧道結(jié)兩側(cè)形成電場,電子主要以場致發(fā)射的方式隧穿膜層,流過單位面積膜層的電流可表示為[12]。

其中q為電子電量,m為電子質(zhì)量,矗為普朗克常數(shù),vx、vy、vz分別是電子在x、y、z方向的隧穿速度,T(x)為電子的隧穿概率。又任意勢壘的電子隧穿概率可表示為[13]

其中jin、jout。分別是進(jìn)入膜層和穿過膜層的電流密度,,x指向?yàn)樾酒姌O表面到壓焊點(diǎn),為膜層中z方向任意點(diǎn)的勢壘,E是垂直芯片電極表面速度為vx電子的能量。

評論