基于Verilog HDL語言的CAN總線控制器設(shè)計及驗證

接著使用ModelSim軟件對所設(shè)計的各個模塊和整個CAN總線控制器進(jìn)行了功能仿真,仿真結(jié)果表明達(dá)到了設(shè)計目標(biāo)。

2 測試驗證

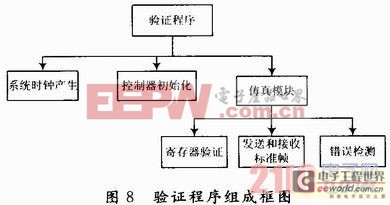

本文最后設(shè)計了CAN總線控制器的測試程序,其目的是模擬一塊微處理器對CAN總線控制器進(jìn)行讀寫操作,從而實現(xiàn)對CAN總線控制器的寄存器訪問,完成總線收發(fā)功能。在該測試程序編寫中,各個功能基本上以任務(wù)的形式實現(xiàn),進(jìn)行不同的仿真時只需調(diào)用相關(guān)的任務(wù)模塊。圖8為驗證程序的組成框圖。

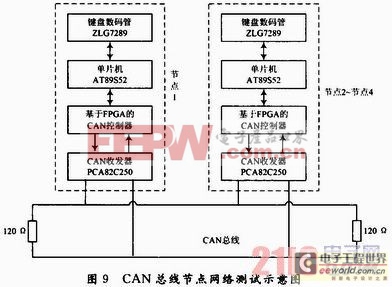

仿真驗證完成以后將其HDL CAN總線程序下載到FPGA中進(jìn)行測試,目標(biāo)芯片采用Cyclone系列的EP1C6Q240C8,為了驗證所設(shè)計的FPGA CAN總線控制器,還設(shè)計了一款基于該FPGA的CAN總線控制器的節(jié)點電路,然后利用所設(shè)計的節(jié)點電路與其他3個利用SJA1000作為控制器的CAN總線節(jié)點進(jìn)行了通信測試。所有的節(jié)點使用AT89S52單片機作為節(jié)點微處理器,PCA82C250作為收發(fā)器,測試結(jié)果表明下載到FPGA中的控制器程序工作正常,實現(xiàn)了預(yù)計的CAN總線通訊功能。測試網(wǎng)絡(luò)示意圖如圖9所示。

測試時,按動節(jié)點1上的開關(guān)并將該狀態(tài)發(fā)送到節(jié)點2,在節(jié)點2上能顯示對應(yīng)的狀態(tài),反之也可。同時也可在節(jié)點2通過鍵盤輸入某一代碼,而在節(jié)點1上的數(shù)碼管上顯示相應(yīng)的結(jié)果。該實驗結(jié)果表明下載到FPGA中的控制器程序工作正常。

3 結(jié)語

本項目利用Verilog HDL語言設(shè)計了一款CAN總線控制器芯片,并使用ModelSire軟件對所設(shè)計的CAN總線控制器進(jìn)行了功能仿真;之后為了驗證設(shè)計,還編制一個驗證程序,并將驗證之后的設(shè)計配置到了FPGA中;最后用所設(shè)計的基于FPGA的CAN總線控制器制作了CAN節(jié)點,并與其他采用SJA1000為控制器的CAN節(jié)點進(jìn)行了通訊測試,實現(xiàn)了CAN總線良好的工作,驗證了設(shè)計的正確性。

評論