基于Verilog HDL語言的CAN總線控制器設計及驗證

CAN_Core為CAN協議控制器的核心部分,完成CAN協議中的數據鏈路層的全部功能以及物理層的部分功能,包括LLC子層的接收濾波、超載通知和恢復管理、MAC子層的數據封裝/拆裝、幀編碼、媒體訪問管理、錯誤檢測、錯誤標定、應答和串行化/解串行化、以及物理層的位編碼/解碼、位定時和同步。CAN_Registers為一寄存器組,外部微處理器可以通過地址直接訪問這些寄存器。根據功能框圖,設計了CAN總線控制器的程序結構,如圖3所示。

1.3 CAN總線各個功能模塊的設計

1.3.1 CAN_IML設計

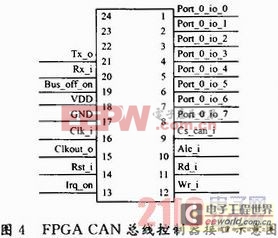

參照SJA1000,設計FPGA CAN總線控制器的接口,如圖4所示。

圖中Port_0_io_7到Port_0_io_0為地址/數據復合總線。Cs_can_i為片選輸入信號。當Cs_can_i為0時允許訪問CAN總線控制器。Ale_i為1時,允許對寄存器進行賦值。Rd_i和Wr_i為微處理器的讀使能信號和寫使能信號。Irq_on為中斷輸出信號,用于中斷微處理器。Rst_i為復位輸入,用于復位CAN接口。Clkout_o為FPGA CAN控制器提供給微處理器的時鐘輸出信號,時鐘分頻寄存器可禁止該引腳輸出。Bus_off_on控制總線關閉和總線開放接口,Tx_o和Rx_i與收發器相連,向總線發送和接收數據。

1.3.2 CAN_Registers設計

設計的CAN總線控制器的寄存器模塊包括以下寄存器:模式寄存器、命令寄存器、狀態寄存器、中斷寄存器、中斷使能寄存器、總線定時寄存器0~1、仲裁丟失捕獲寄存器、錯誤代碼捕獲寄存器、錯誤報警限制寄存器、接收錯誤計數器、發送錯誤計數器、驗收代碼寄存器0~3、驗收屏蔽寄存器0~3、接收信息計數器和接收/發送緩沖器。

1.3.3 CAN_Core設計

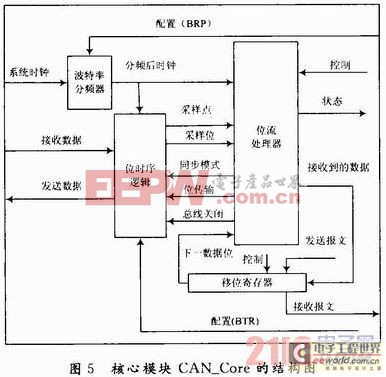

CAN_Core為整個CAN控制器的核心,負責處理CAN的協議。核心模塊由4個部分組成,結構如圖5所示。

下面簡單介紹CAN_Core模塊中的位流處理器、位時序邏輯。

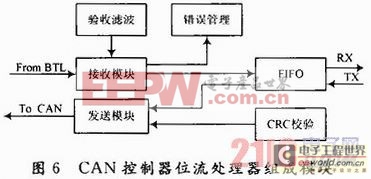

位流處理器是CAN總線控制器中控制數據流的發生器。它還執行總線上的錯誤檢測、仲裁、填充和錯誤處理等功能。主要有接收模塊、發送模塊、錯誤管理模塊、CRC校驗、驗收濾波、FIFO等6個模塊組成,如圖6所示。其中CRC校驗、FIFO、驗收濾波在所執行的項目中已經有他人設計完成。

位時序邏輯的設計包括位定時設計、采樣點設計、位同步設計3部分。下面以定位時為例介紹其設計。

位定時設計 在位定時設計中采用了一個有3個狀態的狀態機。3個狀態分別對應的是同步段和相位緩沖段1以及相位緩沖段2。傳播段占用的時間短,在控制上沒有特別的意義,僅作為物理層的傳播延時,所以沒有設計進狀態機,位定時部分的狀態機設計如圖7所示。

評論