等離子處理提高65nm邏輯器件可靠性

實驗

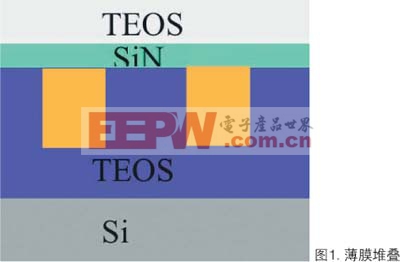

圖1示出了Cu雙大馬士革薄膜堆疊。PECVD TEOS淀積在空白Si襯底上,形成Cu通孔。用PVD淀積TaN/Ta層,作為接觸勢壘。PVD Cu用來作為隨后淀積電鍍(ECP)Cu薄膜的籽晶層,然后進行化學機械拋光(CMP)去除ECP多余的Cu。接著在400℃時淀積SiN薄膜將Cu覆蓋。最后,淀積TEOS作為SiN上面的鈍化層。淀積薄膜和經后處理的薄膜折射率及厚度的測量是用熱波分光橢圓儀5340c OPTI 探針和KLA-Tencor F5。FTIR頻譜儀和 SIMS分析用來決定體薄膜和Cu/SiN界面的薄膜組分結構。FTIR室在每次測量之間用N2沖洗5分鐘,以減少二氧化碳和水氣的影響。

結果和討論

SiN體薄膜結構效應

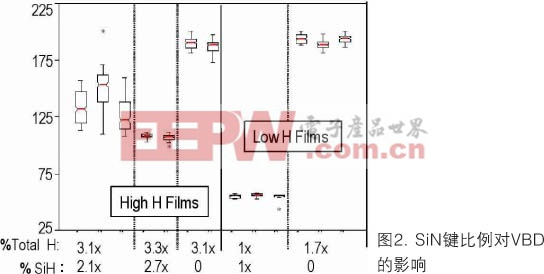

通過優化反應氣體、功率和壓力,在PECVD系統中淀積了二種SiN薄膜:A類是低H含量膜;B類是高H含量膜。線對線擊穿電壓(VBD)測試結果表明,薄膜內H%總含量不影響VBD;但是,Si-H鍵(SiH%)是影響VBD的主要因素。圖2示出的VBD結果說明,良好的VBD性能主要是由于SiN阻擋層薄膜中Si-H鍵的數目減少。

評論