Virtex-5 LXl10的ASlC原型開發平臺設計

通過前期的大量仿真分析可以很好地保證設計的成功率。

(2)后仿真

在PCB Layout完成之后還需要對整個布好的PCB板進行仿真,后仿真更強調對串擾和EMI的分析,如圖7所示。只要任何一個網絡不滿足設計需求,就需要對該網絡進行修改,設計新的走線路徑,直至滿足設計需求。

1.6 電源分布系統(PDS)設計

PDS分析的目的,是要評估數字器件所需的瞬態電流,以提供一條良好的供電路徑。電流路徑中的寄生電感是導致供電網絡設計失敗的根源(例如地彈噪聲)。一種可能的情況是,IC信號應當發生翻轉時卻沒有翻轉;另一種更常見的情況是引起系統抖動(Jitter)變大,從而導致時序錯誤。在兩種情況中,都將造成系統工作不正常或者超出設計規范定義的范圍。

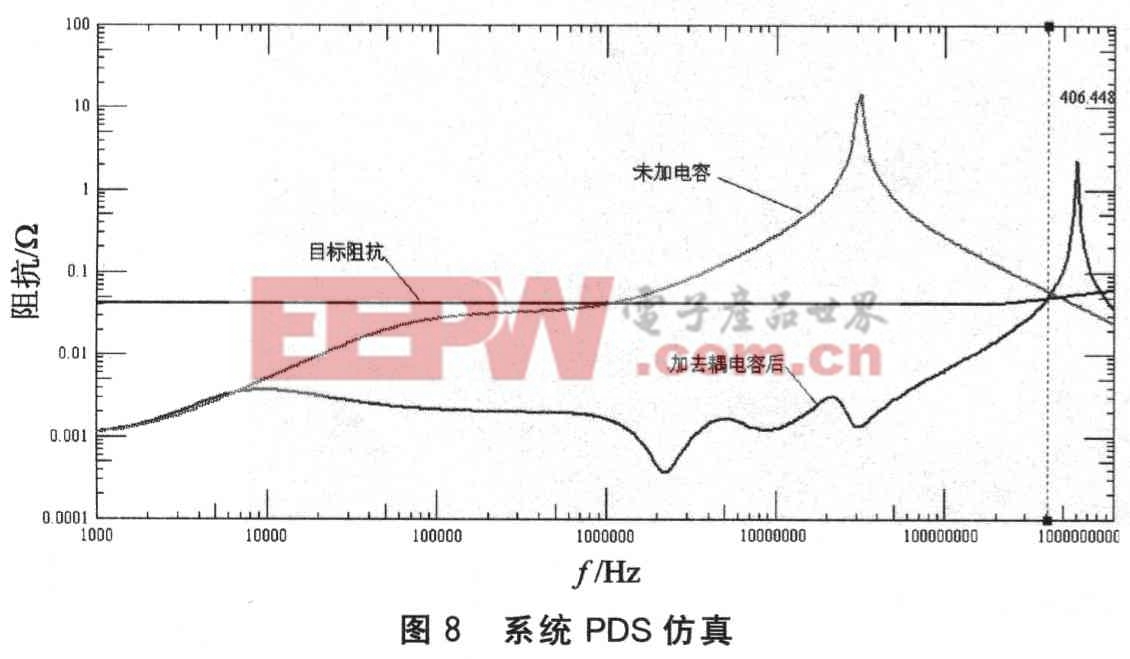

首先檢驗FPGA的靜態和瞬態電流需求,瞬態電流由設計的時鐘域、DCM利用率、開關邏輯數目以及同時翻轉輸出(SimuItaneous Switch Output,SSO)等因素決定,靜態和瞬態電流的大小可以利用XPE或XPower來取得。設計滿足需求的電源去耦網絡,并通過仿真確定所需電容值及其數量,同樣,電容在板上的擺放位置對PDS的影響也很重要。圖8表明了調整前后電源層阻抗的仿真結果。通過對電源去耦網絡的悉心設計,可以有效降低FPGA工作頻率范圍內的電源阻抗。阻抗越低,意味著系統對瞬態電流的需求越能及時做出反應,因此也越能減小電源的供電噪聲。

圖8是對電源VCCO對地的頻率一阻抗曲線的仿真圖。通過對電源去耦網絡的設計,可以保證在400 MHz的范圍內,電源阻抗值是小于目標阻抗的。

1.7 可測試性設計

隨著布線密度的增加,很難對PCB的每個信號都進行物理連接檢測,特別是對于BGA封裝的芯片。另外,對高速信號添加測試點還會導致信號路徑阻抗不連續,引起反射,從而使信號完整性降低。為解決這一矛盾,在設計中首先對FPGA和與其相連的外圍電路的每個信號連接生成了一個測試設計,利用FPGA的邏輯資源對FPGA獲取到的輸入信號與期望的信號值進行比較,對所得的結果通過JTAG端口或者其他外圍顯示電路(如LED)顯示輸出。

2 結 論

本文對驗證平臺硬件設計中的FPGA相關分析進行了詳盡描述。目的是通過設計流程前期的大量分析和仿真,將FPGA在整個設計系統的工作特性以及系統環境對FPGA的影響作用進行模擬,得出的結果轉化為設計約束導人至PCB Layout的環境中,能有效地提高一次設計成功的機率。按照此流程設計的Virtex-5驗證平臺工作正常,達到了預期的設計目的。

評論