Virtex-5 LXl10的ASlC原型開發(fā)平臺設(shè)計

1.4 散熱管理

FPGA支持的速率越高,本身的資源密度越大,因此要關(guān)注應(yīng)用中的散熱管理問題。對FPGA的功率消耗進行估計,以決定是否需要散熱系統(tǒng)。

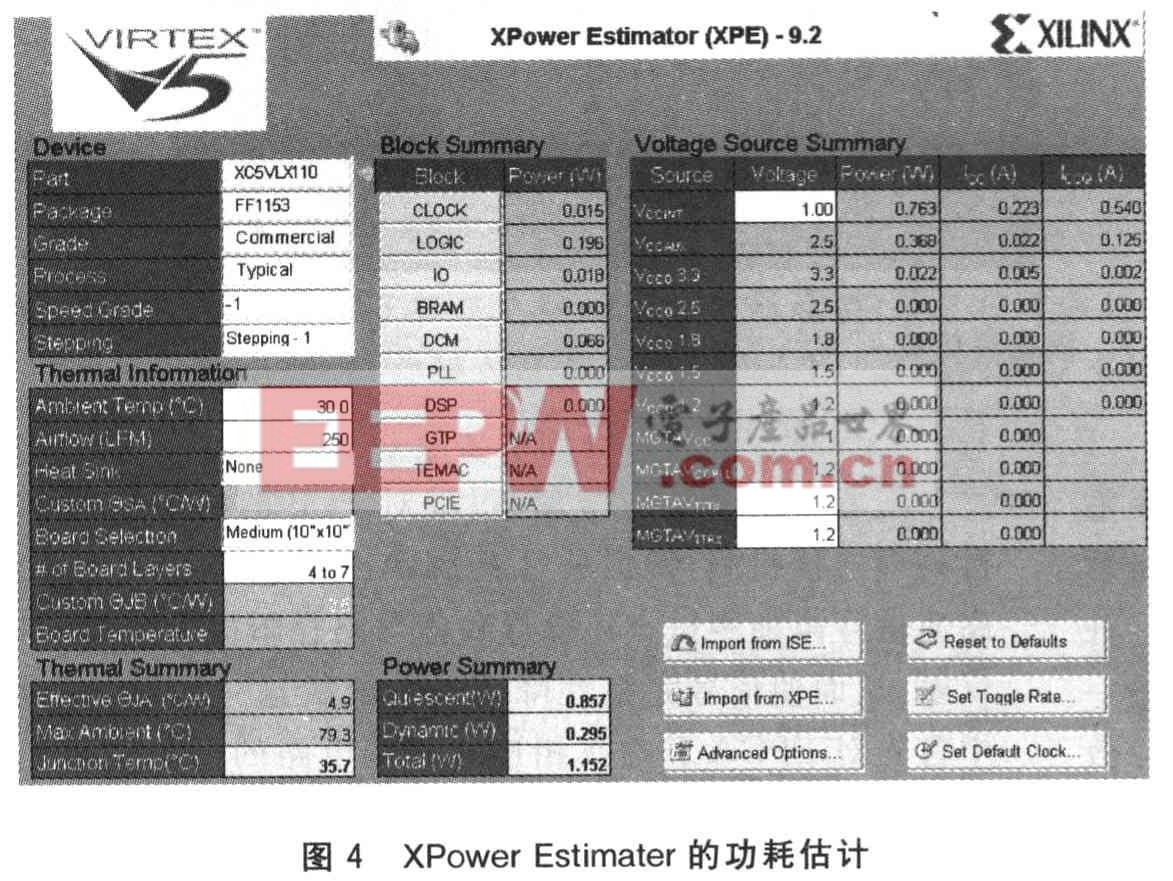

XPower Estimater是一款基于Excel的軟件,通過對設(shè)計資源的利用,包括邏輯資源、DCM、PLL、I/0類型、觸發(fā)率(toggling rate),以及其他與FPGA設(shè)計密切相關(guān)的信息,對FPGA的功耗進行估算。圖4為利用XPE進行設(shè)計功耗估算的截圖。

1.5 信號完整性分析

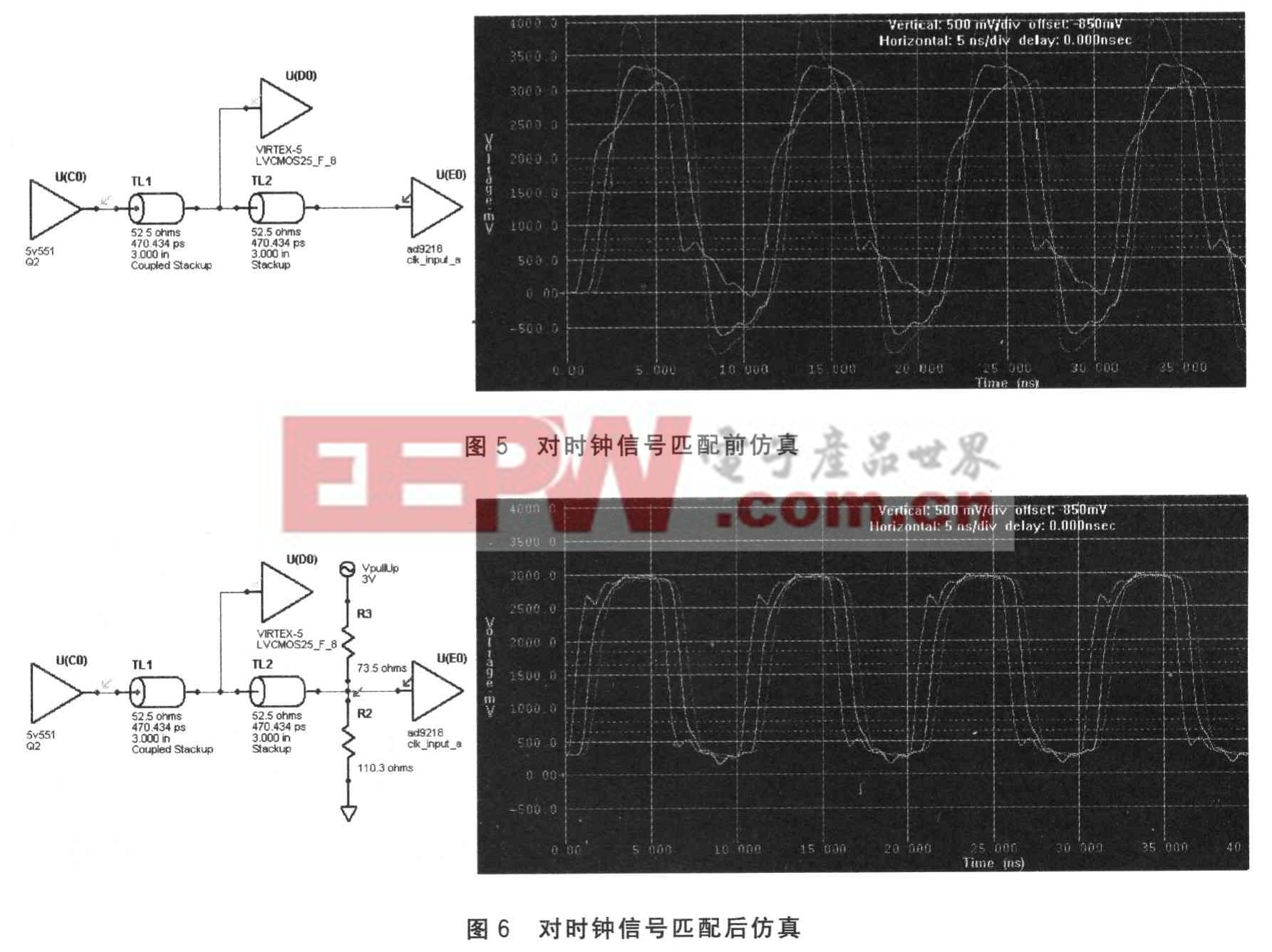

在時域和頻域?qū)υO(shè)計的連接拓撲結(jié)構(gòu)(PCB疊層、驅(qū)動端、接收端、連接器、通孔等等)進行信號完整性分析,目的是要評估和減小信號從驅(qū)動端到接收端的反射、串擾以及EMI/EMC等問題。通過仿真分析得到的約束形式能有效指導(dǎo)PCB布局布線工具進行l(wèi)ayout設(shè)計。進行信號完整性分析,首先要確定與FPGA相接的外圍器件的I/O特性及其約束,進而對FPGA采用何種I/0類型以及端接匹配機制有一個大致的了解,然后是通過仿真對采用的I/O類型及端接電路的各個參數(shù)進行定義及優(yōu)化。

(1)前仿真

S1分析一般主要從高速信號、對時序要求較高的信號、走線最長的信號、負載最多的信號開始,因為這些信號線通常最容易引起SI問題。確定關(guān)鍵信號在仿真環(huán)境中建立起相應(yīng)的拓撲模型。

通過仿真能定義出最長連接走線以及其他滿足噪聲裕量(匹配電路、端接方式等)的網(wǎng)絡(luò)屬性。確定FPGA驅(qū)動緩沖特性,例如I/O標準、驅(qū)動能力以及回轉(zhuǎn)率,使信號完整性問題、EMI/EMC問題最小化,同樣也對接收端I/0屬性進行定義。進行串擾仿真以保證相鄰走線不會引起串擾問題。定義端節(jié)匹配方式。

圖5、6是對時鐘網(wǎng)絡(luò)匹配前和匹配后進行的仿真圖形對比。

評論