Virtex-5 LXl10的ASlC原型開發平臺設計

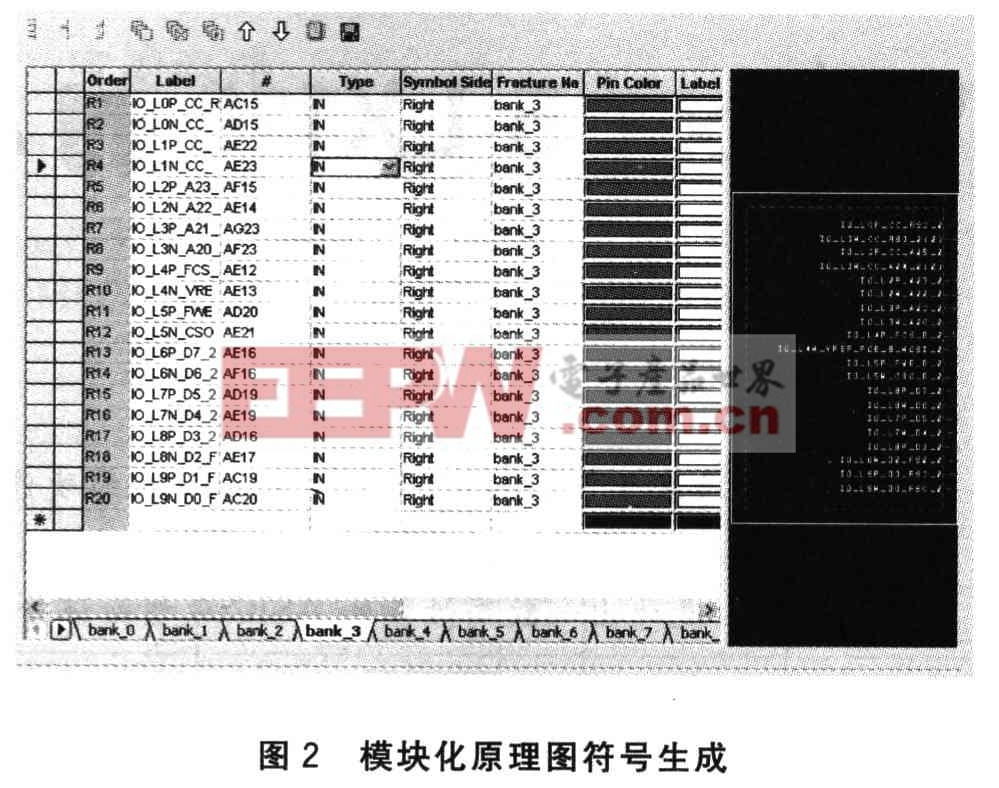

接下來為FPGA創建結構化的原理圖符號。由于FPGA本身I/0的復雜性和可配置性,將整個FPGA分割為多個子模塊能夠有效地減輕設計的復雜度,也便于管理和檢查。圖2顯示了利用Mentor Dxdesigner’原理圖符號生成向導生成模塊化原理圖符號的設計過程。原理圖符號生成之后就可以在原理圖設計環境進行原理圖的設計,指定各個模塊的連接關系。

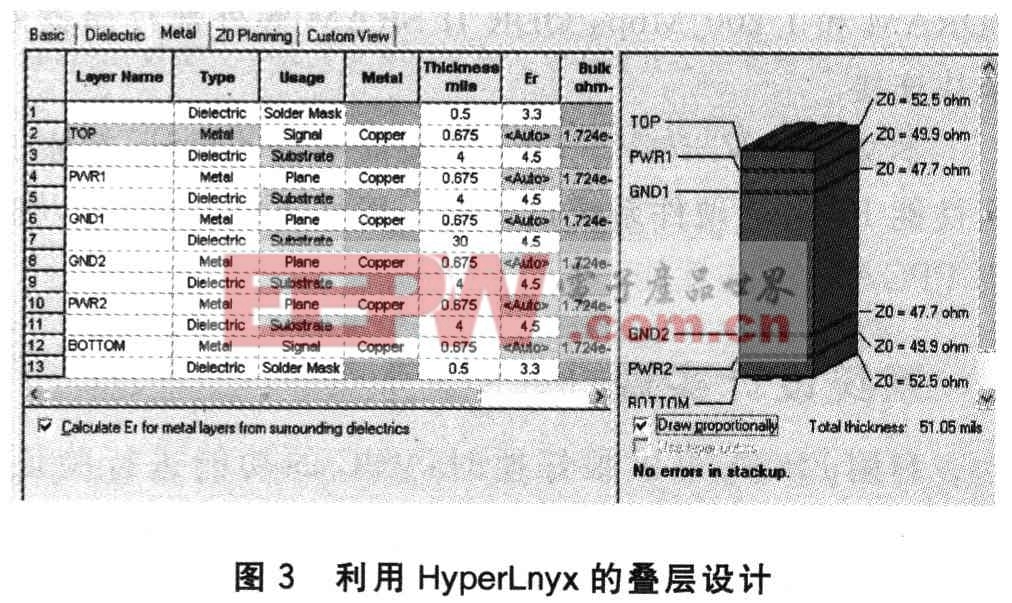

1.3 PCB疊層定義

對。PCB疊層、材料和尺寸的設計需要考慮以下因素:

◆走線層的數量需要考慮到封裝特性、設計所用的I/()數目以及間距;

◆芯片互聯線的數據傳輸速率,信號的上升、下降時間對PCB材料、尺寸以及走線方式和制板工藝的限制;

◆元件所需的不同供電和參考電壓,對電源層的規劃和設計;

◆成本問題(利用盲孔、盲埋孔、微通孔等工藝能有效地減少疊層數目,以達到降低成本的目的)。

該設計中,與FPGA互聯的信號線約為130條,包括配置電路信號線、時鐘信號線及其他I/O信號。選用上下兩個走線層。考慮到多個電源供電,設置2個電源平面、2個地平面。整個PCB采用6層板結構設計,信號層目標阻抗50 Q。

利用HyperLnyx疊層設計如圖3所示。

評論