對基于FPGA的作戰系統時統的研究與設計

2 中斷控制

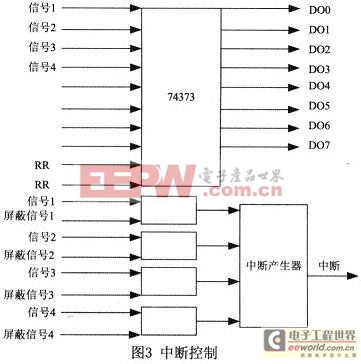

中斷控制部分主要包括脈沖識別、中斷源判斷等。為保證時統信號的準確識別,避免丟幀、誤判,需要對信號整形,適當展寬。在FPGA中利用反相器對信號整形,利用信號上升沿觸發D觸發器輸出高電平去提起中斷,在CPU主板響應中斷后,通過控制D觸發器清零端將輸出的高電平拉低。以此避免非正常情況的出現。

本模塊設計了4路時統接收電路,可同時采集4路外部授時信號,在同時工作的情況下,系統可得到4種不同的時間信息。因此,設計時需要能夠準確地識別4路不同的中斷源。CPCI系統只能分配給每個CPCI設備1個中斷號,使得各路中斷源都要通過這1個中斷號向CPU主板提起中斷。設計過程中可以利用FPGA內部寄存器來識別各路中斷源。見圖3所示。

4路信號用寄存器74373的低4位識別,在系統響應中斷后,隨即讀取寄存器,根據寄存器位的值,判斷是由哪路信號源提起的中斷。屏蔽信號用于系統關斷任一路中斷信號源,根據需要,可用軟件屏蔽l路或多路信號源,未被屏蔽的信號進入中斷產生器,輸出中斷信號,發起中斷申請。

3 守時設計

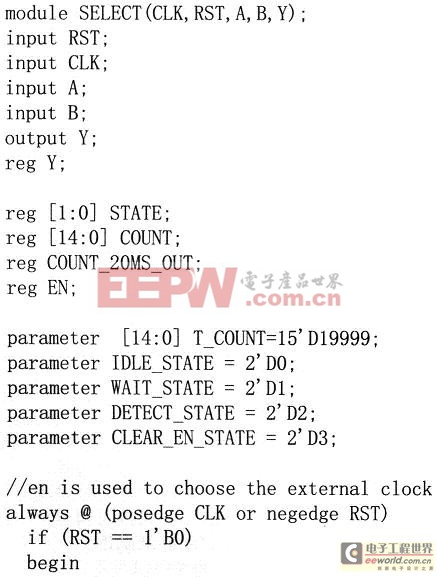

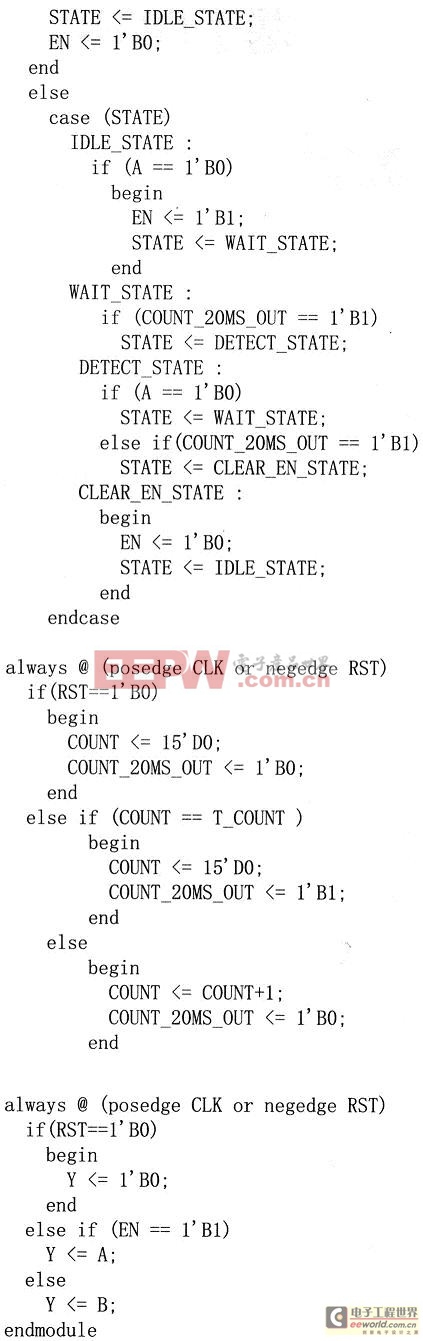

守時是指外部授時信號中斷或受阻時,模塊可以自行產生頻率相同且脈沖沿一致的信號維持系統時間信息。在外部授時信號正常時,由其發起中斷獲得系統時間信息,無外部授時信號時,需由模塊自行產生的信號自動接替外部授時信號的工作,同時用來維持時統信號輸出,保證全系統的時間不中斷。在FPGA中這部分功能由Verilog語言編寫實現。

評論