使用PLD應對產品上市時間和設計靈活性的限制

變化迅速的市場需求驅使越來越多的系統設計者在他們的嵌入式解決方案中使用PLD來緩解產品上市時間的壓力以及設計靈活性需求。該市場傳統上由ASSP和ASIC所主宰。而PLD過去一直被認為是高成本、高功耗的方案。但是,隨著摩爾定律的繼續生效使PLD的單位成本不斷下降,在諸如通信、計算、外設、工業、醫療、消費和汽車等大批量應用中,PLD的靈活性、可編程性和加快上市的固有優點成為可行的ASIC和ASSP替代方案。而且硅工藝和設計優化使PLD可用于廣泛的低功耗應用。

上市時間與設計靈活性

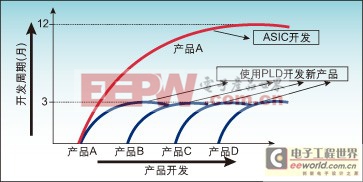

隨著市場需求迅速變化,產品快速上市顯得比過去更加關鍵。最可行的解決方案是縮短開發周期以緩解上市時間的壓力。可編程邏輯可使設計者達此目的。圖1以基于兩者的產品開發周期的比較,說明PLD產品如何有助于新產品的引入。

圖1:產品開發周期

另外,由于產品生命周期的縮短,ASSP的固定功能特性無法滿足產品變化的需求。越來越多的設計者在他們的產品中使用可編程邏輯,通過修改PLD設計和重構器件執行新的操作以開發新功能和標準品。使用可編程邏輯,設計者可以在引入產品時提供幾個不同的版本,以及能在現場對產品進行任意的更新,而無需額外的工程計劃并能降低成本。

生產成本

一般會使用PLD來實現產品原型,然后用ASIC進行量產。然而ASIC開發過程需要很長的開發周期和非常高的一次性工程費用(NRE)。因此,問題就變成到底是用ASIC的投資回報好還是用PLD的投資回報好。(90nm或更先進)工藝的進步使得PLD制造商縮小了與ASIC之間的大批量價格差距。10萬片及以上的128個宏單元或更小的超低密度PLD的批量單價大約為1.5美元。

使用CPLD和FPGA進行設計需要考慮靜態功耗和動態功耗。在大多數

低密度、低功耗CPLD

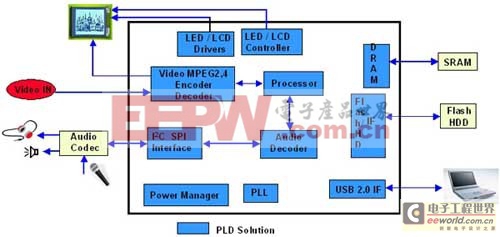

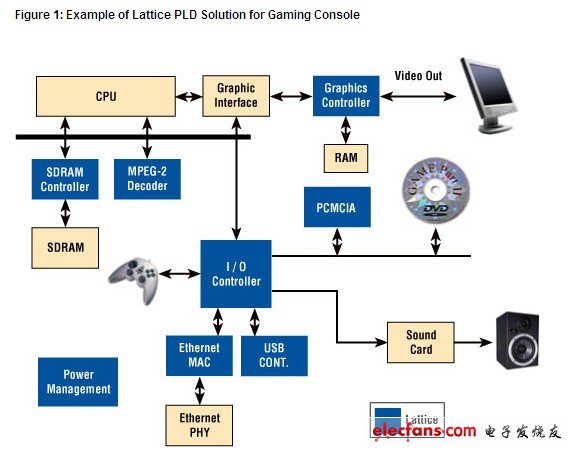

對于較小的設計,例如總線接口、橋接和手持設備(見圖2),使用低功耗、基于閃存的CPLD能提供更低成本的低到超低密度的解決方案。

對于功耗敏感型應用,Lattice半導體公司的ispMACH4000Z(Z表示零功耗)CPLD能提供相當好的低功耗解決方案。

圖2:用Lattice ispMACH4000Z進行PMP設計

由于可從多個供應商那里選擇眾多的器件,因此完全理解設計需求變得尤為重要。下列準則有助設計者選擇合適的CPLD:

1. 靜態和動態功耗的預算是多少?

2. 為了向橋接和接口應用提供總線寬度,所需I/O和邏輯的比值是多少?

3. 該應用的最佳密度和封裝是什么?

4. 輸出所需的電壓容差是多少?

5. 所需的時序裕度是多少?

6. 所選的器件是否現場可編程的,以及開發工具是否容易使用?

7. 有哪些安全性的要求?

不同CPLD供應商有不同的規范和要求,因此選擇合適的器件取決于哪些參數對設計是關鍵的。表1為該器件為匹配設計要求而提供的一組規范。

表1 該器件為匹配設計要求而提供的一組規范

評論