對基于FPGA的作戰系統時統的研究與設計

O 引言

作戰系統時間的統一同步(時統)的重要性越來越得到重視,只有保證整個系統處在同一時間的基準上,才能實現真正意義上的以網絡為中心的信息戰、以精確制導武器系統對抗和以協同作戰方式為主的現代化戰爭。另外由于不同的作戰系統對時統有著不同要求,因此對時統接收處理模塊(簡稱時統模塊)有著較高要求。利用FPGA的強大功能及靈活性設計的時統模塊能夠很好地實現以上要求。

FPGA為大規模可編程邏輯器件,具有編程方便、集成度高、速度快等特點,可反復編程、擦除、使用,在不改變硬件設計的情況下,可實現不同的功能需求。在FPGA中可完成各種時統功能設計。

1 原理

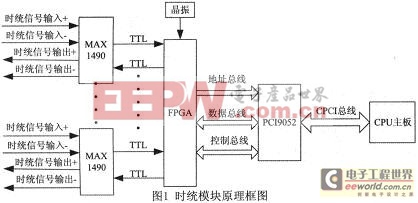

目前時統模塊主要應用于Compact PCI(CPCI)系統,因此該時統模塊為CPCI總線模塊。其主要由總線橋接電路、FPGA、外圍接口電路部分組成,如圖1所示。接口電路采用MAXl490實現對時統輸入信號(授時信號)的接收及轉換。將差分信號轉換成TTL電平信號提供給FPGA處理,另外將FPGA輸出的TTL電平信號轉換成差分信號作為時統信號提供給其它設備。

橋接電路采用PCI9052,實現CPCI總線到局部總線的過渡,并將中斷信號通過CPCI總線的中斷信號線送給CPU主板。CPU主板收到時統模塊的中斷請求后,做出響應,系統軟件根據中斷響應輸出時間信息。

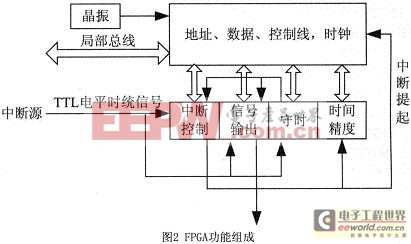

FPGA選用Altera公司MAX70O0S系列中的EPM7256SRl208—10,這是工業界中速度最快的高集成度可編程邏輯器件,具有5000個可用門和1256個宏單元,可滿足設計需要。設計中,FPGA實現了對TTL電平時統信號的各種處理,主要包括中斷控制、信號輸出、守時、時間精度等功能。見圖2所示。

下面具體介紹FPGA內部各主要功能的設計。

評論