對基于FPGA的高斯白噪聲發生器的研究與設計

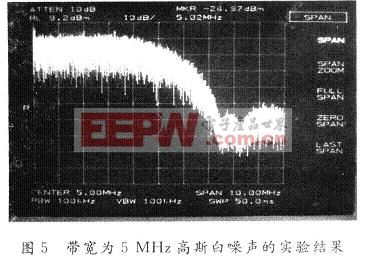

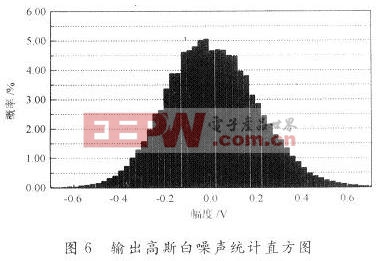

從圖5和圖6可以看出,基于FPGA的m序列發生算法,FIR濾波算法和DDS算法,通過數/模轉換和低通放大后,本文設計的噪聲發生器產生的5 MHz噪聲的3 dB,帶寬為4.8 MHz,帶內平坦度為±1.5 dB,輸出噪聲的統計特性服從高斯分布,滿足了設計需要。

4 結 語

設計了一種基于FPGA高斯白噪聲發生器,分析了該種噪聲發生器所用的m序列發生算法,FIR數字濾波算法和DDS算法,可產生帶寬為3~66 MHz,步進3 MHz,幅度8位可調的高斯白噪聲;采用現場可編程門陣列(FPGA)實現噪聲發生器的設計,在Altera公司的QuartusⅡ軟件環境下,實現了基于FPGA的m序列產生模塊、FIR數字濾波器模塊、DDS模塊和合成模塊,通過數/模

評論