對(duì)基于FPGA的高斯白噪聲發(fā)生器的研究與設(shè)計(jì)

2.3 DDS算法

隨著數(shù)字集成電路和微電子技術(shù)的發(fā)展,直接數(shù)字頻率合成器(Direct Digital Synthesizer,DDS)逐漸體現(xiàn)出其具有相對(duì)帶寬寬,頻率轉(zhuǎn)換時(shí)間短,頻率分辨率高,輸出相位連續(xù),可編程及全數(shù)字化結(jié)構(gòu)等優(yōu)點(diǎn)。

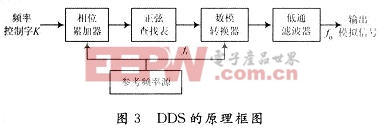

DDS的基本工作原理是根據(jù)正弦函數(shù)的產(chǎn)生,從相位出發(fā),用不同的相位給出不同的電壓幅度,最后濾波平滑出所需要的頻率。圖3是DDS的原理方框圖。

參考頻率源又稱參考時(shí)鐘源,它是一個(gè)穩(wěn)定的晶體振蕩器,用來同步DDS的各組成部分。相位累加器類似于一個(gè)計(jì)數(shù)器,它由多個(gè)級(jí)聯(lián)的加法器和寄存器組成,在每一個(gè)參考時(shí)鐘脈沖輸入時(shí),它的輸出就增加一個(gè)步長的相位增量值,這樣相位累加器把頻率控制字K的數(shù)字變換成相位抽樣來確定輸出合成頻率的大小。相位增量的大小隨外指令頻率控制字K的不同而不同,一旦給定了相位增量,輸出頻率也就確定了。當(dāng)用這樣的數(shù)據(jù)尋址時(shí),正弦查表就把存儲(chǔ)在相位累加器中的抽樣數(shù)字值轉(zhuǎn)換成近似正弦波幅度的數(shù)字量函數(shù)。以上的算法都可在FPGA內(nèi)部實(shí)現(xiàn)。

3 實(shí)驗(yàn)結(jié)果

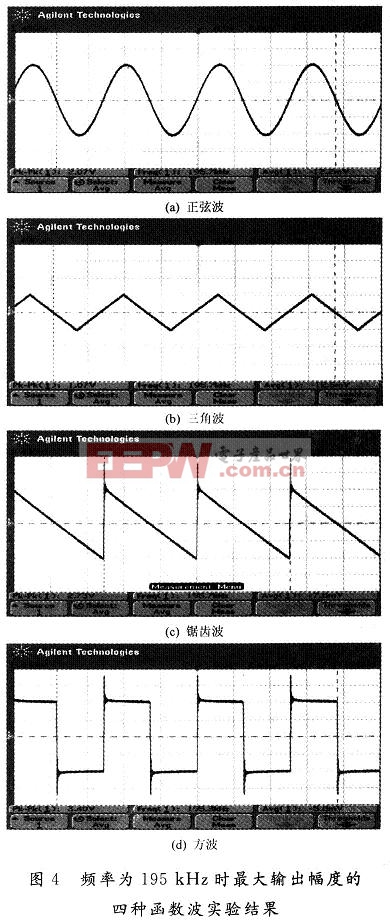

本文的FPGA平臺(tái)選用Altera公司的EP2C8現(xiàn)場可編程邏輯器件,完成所有m序列、FIR數(shù)字濾波和DDS算法,需要FPGA 86%的邏輯單元資源和1%的RAM資源;時(shí)鐘采用50MHz、穩(wěn)定度為50 ppm的有源晶振,通過EP2C8內(nèi)部PLL(Phase Locked Loop,鎖相環(huán))3倍頻到150 MHz作為系統(tǒng)全局時(shí)鐘;采用ADI公司的AD9731進(jìn)行D/A轉(zhuǎn)換,采樣速度150 MSPS,10位;對(duì)AD9731輸出的電流信號(hào)進(jìn)行7階LC低通濾波,然后進(jìn)行放大,使得噪聲信號(hào)的滿幅輸出都達(dá)到峰峰值3V。圖4是頻率為195 kHz最大輸出幅度的四種函數(shù)波測試結(jié)果。

從圖4可以看出,采用DDS模塊,得到了正弦波、三角波、鋸齒波和方波的波形。圖5為該噪聲和函數(shù)波發(fā)生器產(chǎn)生的5 MHz噪聲的實(shí)驗(yàn)結(jié)果,圖6是輸出帶寬為5 MHz的高斯白噪聲統(tǒng)計(jì)直方圖。

評(píng)論