用VHDL實現(xiàn)的有線電視機頂盒信源發(fā)生方案

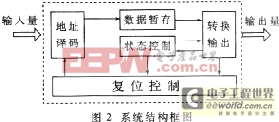

3 系統(tǒng)整體設(shè)計

系統(tǒng)啟動后,主機向I/O口發(fā)出地址信號。AEN為低電平時,系統(tǒng)進行地址譯碼。譯碼成功后,產(chǎn)生一使能信號ENABLE打開數(shù)據(jù)暫存單元。數(shù)據(jù)到來后,數(shù)據(jù)暫存單元將總線上的16位并行數(shù)據(jù)鎖存在暫存器中,同時產(chǎn)生一允許信號PERMIT,允許進行數(shù)據(jù)格式轉(zhuǎn)換。接下來系統(tǒng)根據(jù)當前所處的狀態(tài)進行選擇輸出,完成格式的轉(zhuǎn)換,并產(chǎn)生相應(yīng)的輸出數(shù)據(jù)使能信號DEN和輸出數(shù)據(jù)時鐘信號DCLK。整個過程結(jié)束后,將各信號復位,開始新的轉(zhuǎn)換周期。因此,整個系統(tǒng)應(yīng)包括五個邏輯部分:地址譯碼、數(shù)據(jù)暫存、狀態(tài)控制、復位控制、轉(zhuǎn)換輸出。

3.1 系統(tǒng)的整體框圖

系統(tǒng)的整體框圖如圖2所示。

3.2 系統(tǒng)的工作時序

轉(zhuǎn)換過程的時序如圖3所示。

4 VHDL語言描述

4.1 各單元模塊的描述

- 地址譯碼單元

計算機與I/O設(shè)備間的正確通信是通過對I/O空間的尋址操作來完成的。每個I/O端口都分配了一個地址。在該方案中,將端口的地址設(shè)定為0280H,采用完全譯碼的方式。同時為了避免DMA操作控制總線,設(shè)計時讓aen亦參與譯碼,并由時鐘信號進行觸發(fā)控制。譯碼成功后,產(chǎn)生一使能信號enable(高電平有效),同時將io_cs信號拉低。

- 數(shù)據(jù)暫存單元

enable信號無效時,數(shù)據(jù)暫存單元為高阻狀態(tài)。該信號和寫信號iow(低電平有效)都變?yōu)橛行Ш螅诮酉聛淼囊粋€時鐘的下降沿(確保采樣時數(shù)據(jù)有效),將總線上的數(shù)據(jù)讀入數(shù)據(jù)暫存單元,并產(chǎn)生一允許信號permit,允許系統(tǒng)進行格式轉(zhuǎn)換。

- 狀態(tài)控制單元

這是系統(tǒng)的控制部分。系統(tǒng)狀態(tài)的控制是由系統(tǒng)的控制信號simbol、sign在時鐘信號的驅(qū)動下實現(xiàn)的。系統(tǒng)每完成一次8位數(shù)據(jù)的輸出,在同一時鐘的下降沿,狀態(tài)發(fā)生改變,產(chǎn)生另外一控制信號varb(低電平有效)。復位后,系統(tǒng)又回到初始狀態(tài)。狀態(tài)變化過程如下:

![]()

- 轉(zhuǎn)換輸出單元

轉(zhuǎn)換輸出單元是系統(tǒng)的核心,它包括三個部分:數(shù)據(jù)格式的轉(zhuǎn)換、數(shù)據(jù)使能信號DEN的輸出、數(shù)據(jù)時鐘信號DCLK的輸出。數(shù)據(jù)的轉(zhuǎn)換輸出是由系統(tǒng)當前所處的狀態(tài)決定的。permit信號有效后,在時鐘的上升沿,轉(zhuǎn)換輸出單元檢測系統(tǒng)狀態(tài):狀態(tài)為first時,輸出高8位;狀態(tài)為second時,輸出低8位;狀態(tài)為third時,系統(tǒng)復位,從而完成一次轉(zhuǎn)換,開始下一轉(zhuǎn)換周期。在轉(zhuǎn)換過程中,系統(tǒng)同時完成對信號simbol、sign(低電平有效)的控制。

輸出數(shù)據(jù)使能信號DEN是根據(jù)MPEG-2標準碼流格式產(chǎn)生的,用于數(shù)據(jù)信號的同步。在MPEG-2標準中,碼流是以包的形式傳送的。每一個數(shù)據(jù)包都有一個統(tǒng)一的包標識符PID,它的十六進制形式為47H。從包中的第一個字節(jié)(47H)開始,DEN變?yōu)橛行Вǜ唠娖剑⒈3值降?88字節(jié)。在接下來的16個字節(jié)時間里,DEN保持低電平。

輸出數(shù)據(jù)時鐘信號DCLK用作解復用單元的采樣時鐘,它是由控制信號sign、permit以及系統(tǒng)當前所處的狀態(tài)控制產(chǎn)生的。為了保證采樣時數(shù)據(jù)保持有效,DCLK的輸出比相應(yīng)的輸出數(shù)據(jù)要延遲半個機器周期。

- 復位控制單元

轉(zhuǎn)換結(jié)束后,需要對系統(tǒng)復位,保證下一轉(zhuǎn)換的順利進行。復位信號的產(chǎn)生取決于三個控制量:系統(tǒng)當前狀態(tài)為third、控制信號varb為低電平、控制信號simbol為高電平。復位后,輸出端為高阻狀態(tài),其他信號均為無效值。系統(tǒng)回到初始狀態(tài)。

評論