基于FPGA的仿真系統數據采集控制器IP核設計

3 系統實現

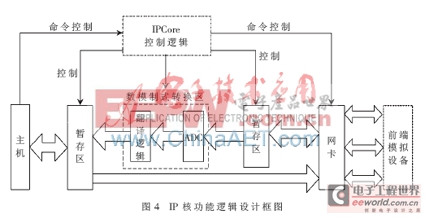

本IP 核功能邏輯的設計基于其任務邏輯定制的基本功能和技術指標。本設計的任務邏輯主要完成對模擬仿真系統前端模擬設備發送指令以及采集前端模擬設備狀態量數據。其功能邏輯也基于發送指令和接收數據兩個數據流來設計,如圖4所示。

為避免高速、高頻系統時序中常存在的競爭、毛刺危險以及建立與保持時間相抵觸等問題,本IP核采用同步設計的方案。同時,為解決實際中仍會經常出現系統產生毛刺和時鐘偏斜等問題。本IP核中擬將時鐘控制改為觸發器輸入允許,將時鐘選擇改為獨立的時鐘分析[7]。

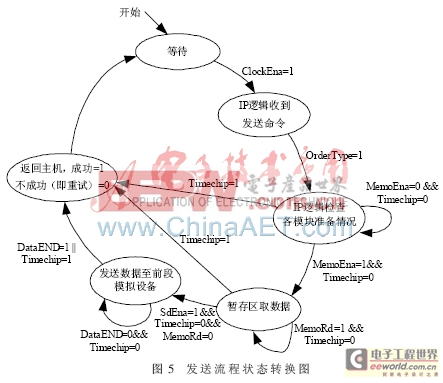

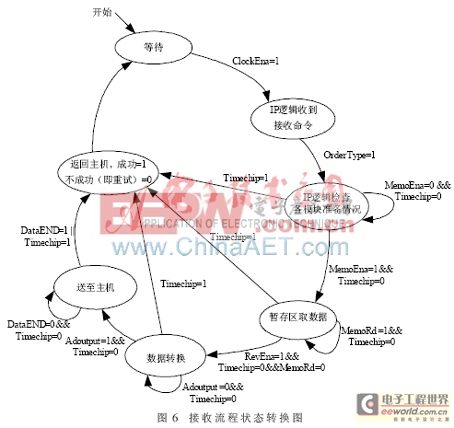

為加快本設計的運行速度及處理效率,本IP核的設計以功能邏輯處理機制為基礎,分別對發送流程和接收流程設計狀態機并實現[8]。

在發送流程的狀態轉換過程中,共有6個狀態,如圖5所示。IP核的控制邏輯判斷來自主機的發送數據命令后,首先檢查其各功能模塊的準備情況,如果準備好,即開始發送數據,從寄存器單元中取出待發送數據并送至網絡通信模塊,由其發送至前端模擬設備。在此過程中,不斷檢測發送完成標志位DataEND,如果該標志位變為有效則表示發送成功,將此信息反饋給主機并進入下一工作周期等待狀態;如果超時該標志位仍未變化,則反饋回主機發送失敗的信息,并請求重發。

相應地,如圖6所示,接收流程的狀態轉換過程有7個狀態。其工作大致與發送流程相同,只是接收數據從寄存器單元讀出后,要先經過數據模式的轉換后,再發送給主機使用。

評論