基于FPGA的仿真系統數據采集控制器IP核設計

現代模擬仿真技術[1]廣泛應用在系統設計、系統分析以及教育訓練中。在模擬過程中,存在大量向前端模擬裝置或仿真模塊發送指令數據,以及從模擬工作設備上讀取狀態參量的情況。在對大型工業設備和系統進行模擬仿真時,數據采集控制的復雜程度愈加惡劣[2]。通過改進數據采集控制器的結構,提高數據采集控制器的自動化和集成化程度,可以有效地提高大型模擬仿真設備數據采集和控制的效率。

FPGA及SoPC技術的發展為此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進行修改和定制,以提高設計效率[3]。本文研究了基于FPGA的數據采集控制器IP 核的設計方案和實現方法,該IP核既可以應用在獨立IC芯片上,還可作為合成系統的子模塊直接調用,實現IP核的復用。

1 系統結構

數據采集控制器主要分為發送機制和接收機制兩部分。在傳統的模擬仿真系統[4]中,發送機制負責將模擬仿真系統主機控制程序模擬運算的數據傳給事先定義的變量,通過專用接口卡將其放在絕對內存地址單元中,再借助智能雙端口的工控機將數據發至前端,以驅動前端設備(如儀表、顯示燈等)進行顯示,或使前端設備(如開關、閥門、步進電機等)進行動作;接收機制與之相反,即實時地將從前端工控機采集的模擬設備的動作量和狀態量(包括模擬實際情況的溫度量、壓力量等)讀到計算機內存地址單元中,并通過專寫程序把這些變量值轉換成主控程序所需要的數據。

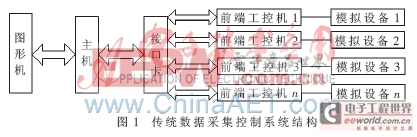

前端設備種類繁多,因此實際中需有針對性地進行設計,以實現工控機對前端設備的控制。此外,工控機與主機之間還必須通過專用接口進行通信,如圖1所示。其結構復雜,不利于設計和調試,同時降低了模擬仿真系統的實時性和效率。

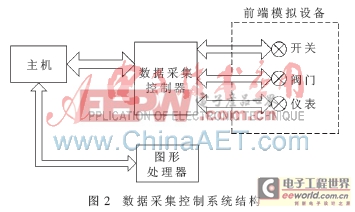

本文設計的IP 核將傳統結構中工控機和接口卡兩級的數據采集控制系統結合起來,設計了一個集成的控制器,由其完全承擔主機與前端設備的數據交換與通信任務。這樣,主機僅負責對整個系統的監控以及對模擬仿真模型的規格運算,而不再分出資源來管理前端模擬設備的控制和數據采集,從而降低了系統的復雜度。結構如圖2所示。

評論