一種基于CPLD的聲發射信號傳輸系統設計

3.3 控制程序設計

pci9054單周期讀、寫和dma讀的vhdl語言時序控制狀態機設計如圖4所示。圖中,s0為空閑狀態。當本地總線請求信號lhold被置1時轉到s1,否則留在s0。s1為總線保持狀態,此狀態下應將本地總線響應信號lholda置1。如ads信號為0且lw/r為1則轉到s3,如ads信號為1且lw/r和blast為0則轉到s4,這種狀態表明此次讀操作為單周期讀。s2為dma讀狀態,在此狀態下應將ready信號和fifo讀使能信號ren1置0。如blast為1,則表明此次dma讀取還未完成,應繼續留在s2,如blast為0,則表明此次dma讀取完成,可轉到s4。s3為單周期寫狀態,此狀態下也要置ready信號為0以表示寫數據有效,并在blast為0時轉到s4。s4為讀寫操作完成狀態,當lhold被置0時,表明pci9054不再請求本地總線,此時應轉到s0,當blast為0且lhold為1時,表明pci9054還要進行數據讀寫,故應轉到s1繼續操作。

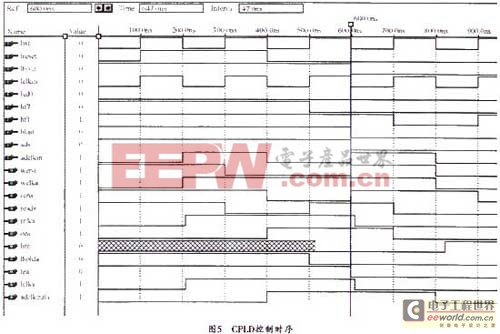

3.4 控制程序邏輯的仿真結果

max+plusⅱ是開發aletra公司的fpga/CPLD系列產品的軟件工具,本設計利用此工具提供的設計環境和設計工具來對cpld控制程序進行開發和調試。其功能時序如圖5所示。

cpld的設計是用vhdl編程實現的。本設計的操作代碼都已經過仿真,并在實際調試中得到應用。

評論