一種基于CPLD的聲發射信號傳輸系統設計

3 cpld邏輯控制

本系統中由于要對高速信號進行處理,因此,對控制信號的時序要求比較嚴格。在控制芯片的選擇上要盡量選用時延小、速度快的芯片。本設計采用美國altera公司的max7000s系列可編程邏輯器件epm7128slc84-15,并采用max+plusⅱ來完成系統的輸入、編譯、驗證及編程,進而完成向量測試及仿真.最后的數據可通過下載線傳輸到芯片中來完成芯片的配置。

3.1 cpld邏輯控制電路

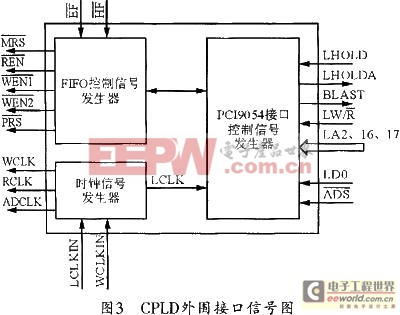

cpld為采樣控制器的核心,數據傳輸所要求的嚴格時序控制關系就由cpld負責處理。它在本系統中主要負責產生與pci9054的握手信號、數據存儲器的片選信號和讀寫控制信號。cpld的外圍信號接口如圖3所示。

cpld可根據fifo存儲器的時序控制要求產生控制信號,并在第一個時鐘周期中將數據分別存入fifo和數據鎖存器74ls373中,而在第二個時鐘周期將鎖存器中的數據再存入fifo,從而完成并行數據向串行數據的轉換。同時根據存儲器的相關信號向pci9054控制器發出中斷請求,并在pci9054讀取數據時產生相應的控制邏輯。

3.2 cpld控制邏輯

當并行數據進入板卡后,cpld首先將一部分數據存入鎖存器,而將另一部分數據直接存入fifo。但此時必須將寫時鐘信號wclk進行二分頻,以便在一個ad轉換周期內完成兩次fifo寫操作。當fifo數據到達半滿時,cpld便向pci9054發出中斷申請,并由pci9054將該申請傳入計算機。若系統響應該中請,則在中斷響應程序內發出讀命令,以讀取字節數和地址信號等。

pci9054通過lhold申請local總線控制權,而cpld則通過lholda響應,以使pci9054能得到局部總線的控制權。pci9054首先將pci地址窄間映射到本地地址空間,接著啟動本地總線的散聚dma周期。cpld收到讀信號(lw/r)、地址選通信號(ads)和地址(la16、la17)后便開始傳送數據。當la16位為0,la17位為1時,系統將使能后三片fifo的讀使能端(ren2),以使后三片fifo數據線上的q0~q31有效而同時也使pci9054的準備好信號(ready)有效,開始數據傳送。在最后一個數據傳送之前,blast信號有效,之后,cpld將在一個時鐘周期后使fifo的讀使能(ren1或ren2)無效,從而完成一次數據傳送過程。

評論