一種基于CPLD的聲發射信號傳輸系統設計

聲發射技術是光纖傳感技術和聲發射技術相結合的產物,是目前聲發射技術的發展趨勢。它將高靈敏度聲發射傳感器安裝于受力構件表面以形成一定數目的傳感器陣列,實時接收和采集來自于材料缺陷的聲發射信號,進而通過對這些聲發射信號的識別、判斷和分析來對材料損傷缺陷進行檢測研究并對構件強度、損傷、壽命等進行分析和研究。

在實際的構件檢測中,現場聲源信號通常是在100~800 khz之間的微弱高頻信號,而且材料損傷檢測、聲發射源定位往往需要多個傳感器形成傳感器陣列,而聲發射信號的數據傳輸系統必須達到640 mbps以上的數據傳輸能力;并應具有應付突發或長時間數據接收和存儲能力。本文就是利用CPLD來實現對聲發射信號的采集,從而有效解決了數據的實時傳輸和存儲問題。

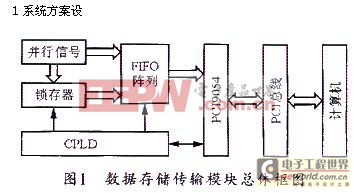

1 系統方案設計

本方案采用fifo存儲器構成外部大容量數據緩沖區,而使用pci總線的dma傳輸方式與微機進行高速數據傳輸。現場聲發射信號經過ad轉換和驅動電路驅動后進入pci板卡,然后將部分數據鎖存,同時將并行信號轉換為串并行信號,通過cpld控制邏輯電路存入fifo。當fifo存儲器中的數據到達一定狀態時,cpld控制

2 fifo數據存儲電路設計

fifo是一個先人先出的雙口緩沖器,為保證整個系統正常工作,fifo存儲器允許系統進行dma操作,以提高數據的傳輸速度。否則,數據傳輸將達不到傳輸要求,而且會大大增加cpu的負擔,甚至無法同時完成數據的存儲。

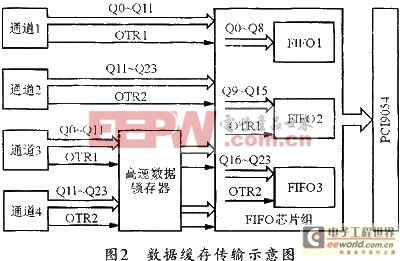

本設計在數據傳輸系統中采用了六片idt72281芯片來緩存數據,并將其分成兩組,其中由三片fifo進行字寬擴展,圖2所示是其緩存傳輸示意圖。按照這種設計,其字寬可達27位,可以傳輸24位數據和兩個otr位。

評論