基于FPGA的寬帶數字接收機變帶寬數字下變頻器

變帶寬數字下變頻器(VB-DDC)可以對多種帶寬的輸入信號進行處理,因此在雷達、通信、電子偵察等領域有廣泛應用。商用數字下變頻器,如Intersil公司單通道DDC HSP50214B,雖然可以實現處理帶寬可變,但是其最高輸入數據采樣率只有65 MHz[1],而且由于其采用多級級聯積分梳狀濾波器(CIC)的傳統下變頻結構,處理帶寬不超過1 MHz,不適合作為寬帶數字接收機的數字下變頻器。基于多相濾波結構的寬帶DDC可以處理寬帶信號,但是處理帶寬一般固定,而且當需要處理信號的帶寬很窄時,因為抽取因子變大,所需乘法器數目增多,因乘法器的工作頻率降低,所以其資源利用率很低。

本文基于Altera公司的Stratix II EP2S60F672C4設計的VB-DDC,結合傳統數字下變頻結構與多相濾波結構的優點,實現了對輸入中頻信號的高效高速處理,同時可以在較大范圍內對信號處理帶寬進行靈活配置。當A/D輸出中頻信號采樣率為100 MS/s時,本文設計的這種VB-DDC信號處理帶寬可在40 MHz~8 kHz的范圍內靈活配置,輸出基帶信號數據率可在50 MS/s~112 kS/s的范圍內變化。

1 系統結構

本文設計的VB-DDC用于如圖1所示的寬帶數字接收機中頻處理系統中,該系統硬件主要由1片FPGA(Altera公司Stratix II 系列的EP2S60F672C4)、AD公司的寬帶A/D轉換器AD6645(14 Bit,最高采樣率達105 MS/s)[2],以及TI公司的達芬奇系列數字信號處理器TMS320DM6437組成。

系統數據流程如圖1所示,A/D采樣的中頻模擬信號輸出至FPGA,FPGA中的VB-DDC將中頻信號下變頻至基帶,再通過McBSP接口將基帶信號傳給DSP進行解調、功率譜估計等數字信號處理,最后DSP再將結果通過以太網送至上位機PC進行顯示。同時,VB-DDC可通過McBSP接口接收上位機PC傳來的配置參數,實現DD動態配置。

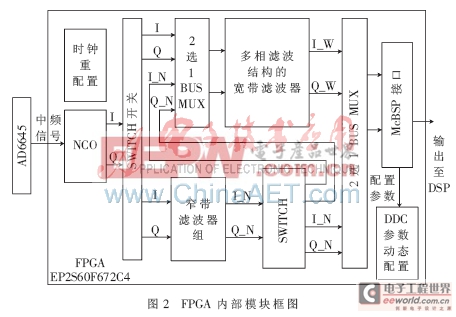

本文主要討論該系統中的FPGA部分,其內部各模塊框圖如圖2所示。

評論