一種基于FPGA的多時鐘片上網(wǎng)絡(luò)研究與設(shè)計

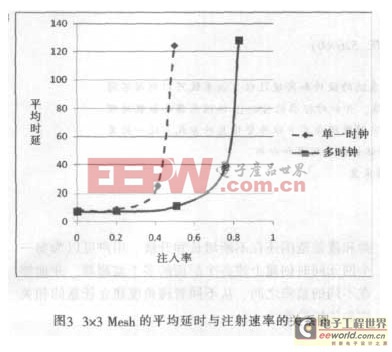

為了*估所設(shè)計的多時鐘架構(gòu)的性能, 將利用所設(shè)計的路由器的VHDL 模型,模擬一個3×3Mesh 結(jié)構(gòu),在本身頻率下執(zhí)行包裝產(chǎn)生的數(shù)據(jù)包。路由器的頻率值會在拓撲結(jié)構(gòu)合成,布局和布線階段完成之后得出。對于不同的配置(資源的可用性、跨路由器的距離、bRAM/dRAM FIFO 的版本),路由器的頻率可以降低高達18%[6]。圖3 顯示了單一時鐘與多時鐘,在延時與注射速率關(guān)系中的曲線圖。在單一時鐘時,網(wǎng)絡(luò)的頻率為286MHz。而在多時鐘時, 頻率的范圍是從286MHz~357MHz。圖3 中,X 軸表示的注射率是在一個周期內(nèi)每個節(jié)點注入flit 的數(shù)量。Y 軸曲線測量的是每個實例中數(shù)據(jù)包的平均延時。可以看出,所提出的多時鐘片上網(wǎng)絡(luò)相比單一時鐘片上網(wǎng)絡(luò)的性能顯著增加。

4 結(jié)語

本文介紹了一個基于FPGA 的高效率多時鐘的虛擬直通路由器,通過優(yōu)化中央仲裁器和交叉點矩陣,以爭取較小面積和更高的性能。同時,擴展路由器運作在獨立頻率的多時鐘NoC 架構(gòu)中,并在一個3×3Mesh 的架構(gòu)下實驗,分析其性能特點,比較得出多時鐘片上網(wǎng)絡(luò)具有更高的性能。

評論