一種基于FPGA的高速通信系統(tǒng)研究與設(shè)計

3.2 異步時鐘域變換

系統(tǒng)輸入信號工作在不同的異步時鐘域,需要在FPGA內(nèi)部將信號變換到同一個時鐘域。

串口信號速度低,可以使用系統(tǒng)時鐘高速采集的方式。根據(jù)奈奎斯特抽樣定律,抽樣頻率大于2倍信號最高頻率,就可以從抽樣信號中無失真地恢復(fù)原信號。本系統(tǒng)使用高于5倍串口波特率的時鐘去采集串口數(shù)據(jù)。經(jīng)過誤碼儀的大量測試,串口數(shù)據(jù)能夠被正確接收和恢復(fù)。

視頻信號是并行信號,采用高速采集的方法會增加數(shù)據(jù)量,不適合本系統(tǒng)。本系統(tǒng)采用雙口FIFO完成異步時鐘域轉(zhuǎn)換。S3C500E片內(nèi)的Block RAM資源可以靈活的生成雙口FIFO,與普通邏輯單元生成的雙口FIFO相比,它的穩(wěn)定性高,最高讀寫速度快,產(chǎn)生亞穩(wěn)定狀態(tài)的概率小。雙口FIFO的輸入端連接系統(tǒng)輸入信號的時鐘和數(shù)據(jù);在輸出端連接系統(tǒng)時鐘數(shù)據(jù)。雙口FIFO的讀取時鐘速度必須高于寫入速度,以避免FIFO存滿后溢出導(dǎo)致有效數(shù)據(jù)丟失。另一方面,慢時鐘域向快時鐘域轉(zhuǎn)換的時候,F(xiàn)IFO會出現(xiàn)讀取空的狀態(tài),此時將取出無效數(shù)據(jù)(這些數(shù)據(jù)是FIFO中最后一個數(shù)據(jù)的重復(fù))。無效數(shù)據(jù)通過串行數(shù)據(jù)幀傳輸?shù)浇邮斩耍瑫?dǎo)致恢復(fù)后輸出信號出現(xiàn)誤碼。所以系統(tǒng)將FIFO的空標志empty信號添加到數(shù)據(jù)幀,用于識別無效數(shù)據(jù)。

3.3 數(shù)據(jù)組幀及編碼

同步傳輸需要將原始數(shù)據(jù)組成數(shù)據(jù)幀再進行發(fā)送,即在數(shù)據(jù)間添加起始位、停止位和校驗位。數(shù)據(jù)幀的起始位過長會影響傳輸效率,過短會增加接收端識別的難度。本系統(tǒng)選用80 b為一幀,起始位為8 b,停止位為2 b,奇校驗位為1 b。接收端邏輯通過對多個數(shù)據(jù)幀分析后,定位數(shù)據(jù)幀的起始位。由于每幀數(shù)據(jù)長度固定,所以找到某一幀的起始位后可以周期性的計算出接下來各幀的起始位置,不再需要反復(fù)做識別工作。

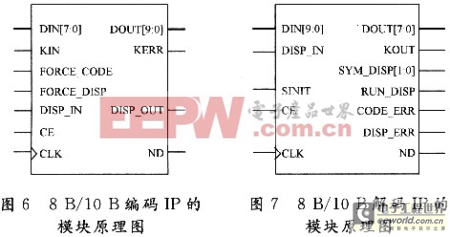

數(shù)據(jù)組幀后信號的平均位速率可能低于CLC012的最低工作頻率,不能直接用于傳輸,還需要對其進行8B/10B編碼。8B/10B技術(shù)是將8個數(shù)據(jù)位經(jīng)過某種映射的機制轉(zhuǎn)化為10個數(shù)據(jù)位的字碼,可使發(fā)送的“O”、“1”數(shù)量保持一致,連續(xù)的“1”或“0”基本不超過5位。8 B/10 B編碼技術(shù)保證了傳輸?shù)腄C平衡,增加了信息傳輸?shù)目煽啃浴O到y(tǒng)使用Xilinx公司提供的8 B/10 B編碼和解碼IP核,減少了系統(tǒng)的開發(fā)周期,增加了系統(tǒng)的穩(wěn)定性。8 B/10 B編碼及解碼IP的模塊原理圖如圖6和圖7所示。

4 結(jié)語

介紹了一種基于FPGA的高速通信系統(tǒng),通過電纜驅(qū)動器和接收均衡器,拓展了LVDS信號的傳輸距離。經(jīng)過測試,使用同軸電纜的傳輸距離達到200 m,單個通道傳輸速率達到120 Mb/s。FPGA的可重構(gòu)性使系統(tǒng)靈活多變,可以適應(yīng)不同的應(yīng)用需求。

評論