基于FPGA和頻率合成器的GPS信號源的設(shè)計

頻率合成器是發(fā)射系統(tǒng)和接收系統(tǒng)中的核心器件,采用相位負反饋頻率控制技術(shù),具有良好的窄帶載波跟蹤性能和帶寬調(diào)制跟蹤性能,為系統(tǒng)上、下變頻提供本振信號,對相位噪聲和雜散具有很好的抑制作用,通過鎖相頻率合成技術(shù)實現(xiàn)的頻率源已經(jīng)在雷達、通信、電子等領(lǐng)域得到了廣泛應(yīng)用。

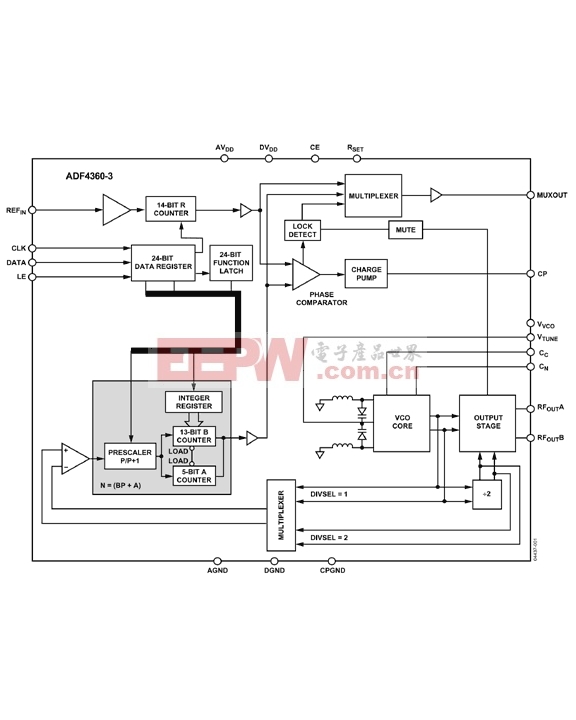

本文以GPS信號源設(shè)計為參考,介紹ADI公司的頻率合成器ADF4360-4在GPS信號源設(shè)計中的典型應(yīng)用。

1 信號源系統(tǒng)組成

1.1 系統(tǒng)設(shè)計

根據(jù)文獻了解了GPS信號的結(jié)構(gòu)特點,本文設(shè)計GPS信號源的目的是模擬衛(wèi)星發(fā)射的GPS信號,也就是對GPS信號進行基帶調(diào)制并產(chǎn)生頻率為1 575.42 MHz的GPS射頻信號,根據(jù)文獻,在系統(tǒng)總體設(shè)計中,采用超外差上變頻思路,根據(jù)系統(tǒng)設(shè)計特點,分?jǐn)?shù)字電路和模擬電路兩部分,系統(tǒng)設(shè)計如圖1所示,數(shù)字電路部分設(shè)計采用軟件無線電的思路,利用FPGA芯片完成GPS信號的基帶調(diào)制和中頻調(diào)制,輸出8 b的GPS數(shù)字中頻信號,通過D/A器件轉(zhuǎn)換為模擬信號后送到模擬電路;模擬電路部分是整體設(shè)計的核心,主要是進行射頻電路板的設(shè)計與實現(xiàn),采用頻率合成器、混頻器等器件,對信號進行混頻,濾波,功率控制等,將GPS中頻信號混頻調(diào)制到射頻信號,利用射頻電路完成上變頻功能。

1.2 模塊設(shè)計

(1)數(shù)字電路:數(shù)字電路部分就是基帶/中頻模塊設(shè)計,采用軟件無線電思路,根據(jù)文獻,利用FPGA芯片產(chǎn)生GPS導(dǎo)航電文(D碼)、C/A碼、數(shù)字中頻載波,對它們進行基帶調(diào)制、擴頻調(diào)制輸出GPS數(shù)字中頻信號,其中GPS信號調(diào)制原理如圖2所示,主要由C/A碼模塊、D碼模塊、DDS模塊和調(diào)制模塊等組成。其中C/A碼模塊產(chǎn)生速率l.023MHz的第i顆衛(wèi)星的C/A碼序列,C/A碼有1 023個碼片,持續(xù)周期是1 ms;D碼模塊產(chǎn)生速率50 Hz的第i顆衛(wèi)星的導(dǎo)航電文(D碼);DDS模塊產(chǎn)生速率12.5 MHz的數(shù)字載波信號;調(diào)制模塊對C/A碼、D碼和載波信號進行擴頻調(diào)制和BPSK調(diào)制,輸出12.5 MHz的GPS數(shù)字中頻信號。

(2)模擬電路:根據(jù)文獻,模擬電路部分就是射頻模塊設(shè)計,利用頻率合成器、混頻器、濾波器和衰減器等器件進行射頻電路設(shè)計,基本原理如圖1所示的模擬部分,功能是將GPS信號由中頻搬移到射頻上,通過濾波器濾波,經(jīng)可調(diào)衰減器調(diào)整功率后輸出GPS射頻信號,完成上變頻功能。

評論