一種基于FPGA的高速通信系統研究與設計

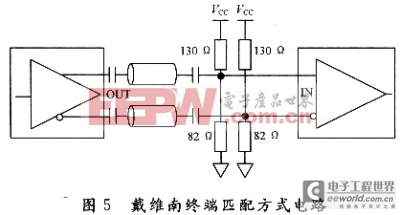

LVDS驅動器由恒流源構成,因此需要做終端匹配。通常情況下在輸入端并聯100 Ω電阻從而滿足互聯系統要求的差分阻抗。在強噪聲環境下,交流耦合連接時可以采用戴維南終端匹配方式提供1.2 V的偏置電壓,同時滿足100 Ω差分阻抗的設計要求。具體方法是將LVDS的+/-端通過130 Ω電阻上拉至VCC,同時下拉82 Ω電阻到地,如圖5所示,電阻精度要求在1%。

2.3 電路PCB設計

在PCB設計過程中,要注意電路板的布局。模擬電路和數字電路需要分開,使用單點接地的方式相連。將邊沿速率變化快的VTTL/LVCMOS信號與LVDS信號布在不同信號層上,并用電源和底層隔開,減小耦合到LVDS線路上的串擾。LVDS走線要遵循以下規則:

(1)差分對兩根信號從芯片扇出后就盡量靠近(緊耦合),這樣有助于消除反射,確保耦合的噪聲是共模形式。

(2)對內信號的布線長度要保持一致,以減小信號延時,長度匹配控制在10 mil以內。

(3)對內信號保持固定的線間距,避免因為線間距變化導致差分阻抗不連續。

(4)差分對間盡量遠離,減少線間串擾,必要時在差分對間放置隔離用的接地過孔。

(5)盡量減少差分信號線上過孔的個數,避免走90°拐角,使用圓弧或者45°折線代替。

(6)LVDS信號不能跨平面分割,否則會因為缺少參考平面而導致阻抗不連續,要給LVDS信號設置完整的參考平面。

(7)匹配電阻盡可能靠近接收端。

3 系統的邏輯設計

3.1 時鐘部分設計

時鐘信號由電路板上40 MHz晶振提供。通過數字時鐘管理單元DCM鐘倍頻得到120 MHz的系統的工作時鐘。使用DCM模塊時,注意DCM的輸入和輸出需要通過BUFG單元與全局時鐘資源相連。全局時鐘資源使用全銅層工藝實現,并設計了專用時鐘緩沖與驅動結構,使全局時鐘到達芯片內部所有邏輯單元的時延和抖動都為最小。DCM在時鐘鎖定后使能LOCK信號,表示時鐘倍頻工作完成,使用這個信號作為FPGA內部其他邏輯的復位。

評論