一種基于FPGA的高速通信系統(tǒng)研究與設(shè)計

2 系統(tǒng)的硬件設(shè)計

2.1 FPGA部分電路設(shè)計

系統(tǒng)選用Xilinx公司Spartan3系列的FPGA:S3C500E。它有10 476個邏輯單元,232個I/O,4個時鐘管理模塊(DCM),存儲器包括360 Kb的塊RAM和73 Kb的離散RAM。所有I/O可以組成92組LVDS差分對,最高輸入輸出速率高到622 Mb/s,所以系統(tǒng)不需要額外的電路實現(xiàn)LVDS接口。DCM模塊可以將輸入時鐘靈活的倍頻或降頻,最高工作頻率達到311 MHz。以上參數(shù)和性能不僅滿足當前的設(shè)計需求,而且為系統(tǒng)的升級保留了充足的設(shè)計余量。FPGA外圍電路包括時鐘部分和配置部分。時鐘使用電路板上的晶振提供,通過GCLK腳與FPGA相連。GCLK是專用時鐘引腳,這個腳的驅(qū)動能力強,到所有邏輯單元的延時基本相同。配置電路采用主動SPI模式。相比其他模式,主動SPI模式的外圍電路簡單、體積小、成本低。而且SPI FLASH的容量大,除了存儲配置文件,還可以存儲其他用戶數(shù)據(jù)。S3C500E的配置文件大小為2 Mb,本系統(tǒng)采用存儲量為16 Mb的M25P16作為配置存儲器。

2.2 傳輸部分電路設(shè)計

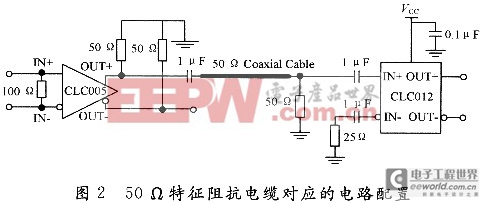

傳輸部分設(shè)計包括選擇同軸電纜和設(shè)計相應(yīng)的發(fā)送接收電路。本系統(tǒng)選用的同軸電纜型號為SVY-50-3,成本低、性能好。這款電纜的特征阻抗為50 Ω,速率150 MHz時信號傳輸100 m的最大衰減為18.01 dB。它具有良好的屏蔽特性,可以在復雜的電磁環(huán)境中正常工作。電纜驅(qū)動電路和接收均衡電路分別選用National Semiconductor公司的芯片CLC005和CLC012。CLC005支持LVDS電平輸入,最高傳輸速率達到622 Mb/s,輸出信號峰一峰值從O.7~2 V。CLC012可以自動均衡頻率在50~650 MHz的信號。時鐘恢復器件選用CLC016,它的輸入信號來自CLC-012,輸出時鐘和數(shù)據(jù)接FPGA,恢復的時鐘在數(shù)據(jù)上升沿有效。CLC005和CLC012用于特征阻抗為75 Ω的傳輸系統(tǒng),針對本系50 Ω特征阻抗的同軸電纜,需要改動外圍電阻配置,否則會因為阻抗不匹配引起信號反射,最終導致信號傳輸質(zhì)量下降。相應(yīng)的配置方式如圖2所示。

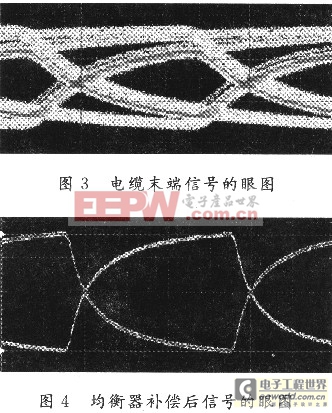

通過測試,此組傳輸器件可以驅(qū)動LVDS信號通過SVY-50-3型號電纜傳輸至少200 m。信號經(jīng)過傳輸后,在電纜末端衰減嚴重,噪聲和抖動也較嚴重。此時信號眼圖如圖3所示,可以看出信號質(zhì)量差。直接接收此信號,會產(chǎn)生信號電平誤判,而且信號的抖動將導致后級電路無法正常工作。接收均衡器CLC012自動為信號損耗提供補償后,信號上的噪聲和抖動均得到了改善,信號的眼圖如圖4所示。

評論