一種基于FPGA的CAN總線通信接口的設計

2.2 SJA1000讀寫數(shù)據(jù)流程控制

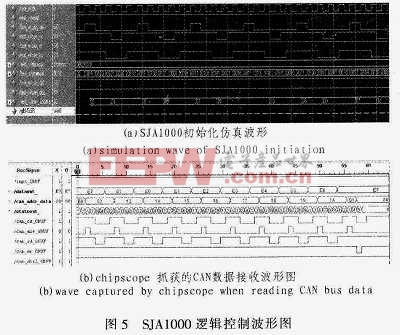

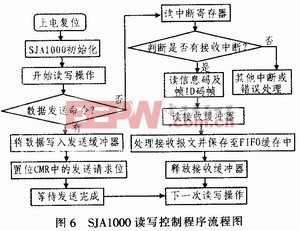

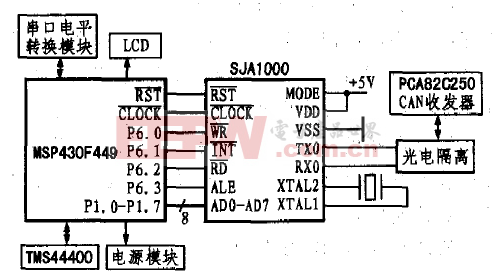

FPGA對SJA1000控制程序包括SJA1000初始化、SJA1000讀數(shù)據(jù)、SJA1000寫數(shù)據(jù)等部分。SJA1000的初始化是在復位模式下進行的,在復位模式下分別設置時鐘分頻器CDR、總線定時器(BTR0、BTR1)、輸出控制寄存器(OCR)等重要寄存器。SJA1000通信波特率由總線定時器決定,需要與后端節(jié)點的波特率相同才能進行節(jié)點間的正常通信。FPGA上電后需要延時一段時間.等待SJA1000復位完成才能進行SJA1000初始化。初始化仿真波形如圖5(a)所示。SJA1000內(nèi)部有一個接收緩沖器和一個發(fā)送緩沖器。FPGA對SJA1000的讀寫操作,實際上對這兩個緩沖器的讀寫控制。當FPGA接收CAN總線數(shù)據(jù)時首先讀取SJA1000中斷寄存器IR判斷是否有接收中斷。如果有接收中斷到來則開始讀取緩沖器內(nèi)的8字節(jié)數(shù)據(jù),然后釋放接收緩沖器(寫命令寄存器CMR)。使用Xilinx公司的Chipseope軟件進行板上測試,測試數(shù)據(jù)為(E0,E1,……E7),抓取到的波形如圖5(b)所示。FPGA讀寫SJA1000的流程控制圖如圖6所示。

2.3 CY7C68013A通信控制程序

CY7C68013A提供一種量子FIFO的處理架構,使USB接口和應用環(huán)境直接共享內(nèi)部含有的4 K FIF0空間。本文CY7C68013A的控制是以異步SLAVE FIFO方式實現(xiàn)的,F(xiàn)PGA對CY7C68013A的邏輯控制實際上是對CY7C68013A內(nèi)部FIFO的異步讀寫控制。設置CY7C68013A端點2為批量輸入端點(FIF0地址為00),端點6為批量輸出端點(FIF0地址為1O)。FPGA判斷CY7C68013A的PA[1:0]端口電平,當PA[1:0]為01時,F(xiàn)PGA將接收到的CAN總線數(shù)據(jù)寫入端點2對應的FIF0空間并上傳給上位機,PA[1:0]為10時,F(xiàn)PGA讀取端點6對應的FIFO內(nèi)數(shù)據(jù)。FPGA對CY7C68013A的時序控制嚴格按照芯片手冊完成。

由于USB數(shù)據(jù)包與CAN數(shù)據(jù)幀是基于兩種不同協(xié)議的數(shù)據(jù)格式,因此在FPGA內(nèi)開辟了2個512x8bit的FIFO緩存,并要進行必要的格式轉換。例如,當從USB總線端注入的數(shù)據(jù)大于8字節(jié)時,需要將數(shù)據(jù)分成多幀傳送給CAN總線;當數(shù)據(jù)小于8字節(jié)時則在數(shù)據(jù)后填充0。另外,在數(shù)據(jù)傳送給CAN總線之前還需要添加適當?shù)膸畔⑴c幀識別碼。

評論