一種基于FPGA的CAN總線通信接口的設計

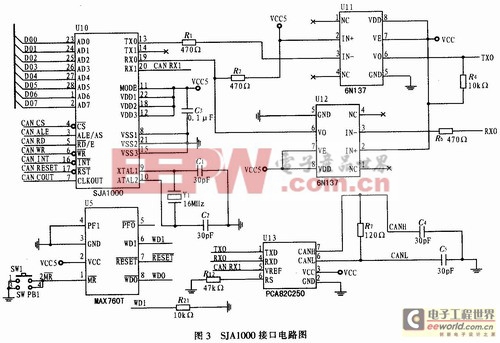

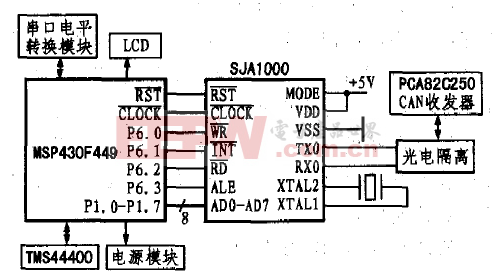

1.2 CAN總線接口電路

選用Philips公司的SJA1000作為CAN控制器,采用PCA82C250作為CAN收發器,并在CAN控制器與收發器之間使用6N137進行光電隔離,以增強抗干擾能力。將MODE引腳接高電平即SJA1000工作在INTEL模式,引腳與復位芯片MAX706T的RESET引腳相連,進行全局復位。在FPGA與SJA1000連接時需要使用741V164245電平轉換器完成CAN總線5 V TTL電平向3.3 V FPGA I/O電平的轉換。另外,SJA1000的RX1引腳與PCA-82C 250的VREF引腳相連,使用輸入比較器旁路功能,可減少內部延時,增加正常通信的總線長度。具體的接口電路如圖3所示。

2 FPGA邏輯控制程序

2.1 SJA1000邏輯控制

由于SJA1000地址線與數據總線復用,FPGA不僅僅要產生SJA1000讀寫控制引腳的信號邏輯,還需要模擬單片機等處理器產生對SJA1000的尋址信號,實際上是一個向SJA1000寫地址的過程。根據SJA1000技術手冊的時序要求,要完成對SJA1000內寄存器的正確讀寫,接口邏輯必須在地址鎖存信號ALE為高電平時將SJA1000的寄存器地址當作數據寫入,然后在ALE和片選信號![]() 為低電平后使能SJA1000的讀寫控制信號(WR或RD)。SJA1000的邏輯控制采用狀態機的方式完成,狀態機流程圖如圖4所示。起始態為IDLE態,當接收到數據讀寫等命令時,進入ADDR-ESS態,向SJA1000寫入相應寄存器的地址值。然后根據命令類型決定下一個態是寫寄存器狀態(WR1~WR3)還是讀寄存器狀態(RD1~RD4)。以寫寄存器為例,在WR1態ALE、

為低電平后使能SJA1000的讀寫控制信號(WR或RD)。SJA1000的邏輯控制采用狀態機的方式完成,狀態機流程圖如圖4所示。起始態為IDLE態,當接收到數據讀寫等命令時,進入ADDR-ESS態,向SJA1000寫入相應寄存器的地址值。然后根據命令類型決定下一個態是寫寄存器狀態(WR1~WR3)還是讀寄存器狀態(RD1~RD4)。以寫寄存器為例,在WR1態ALE、![]() 、

、![]() 等信號置為非有效態。將

等信號置為非有效態。將![]() 置為有效狀態;在WR2態ALE、

置為有效狀態;在WR2態ALE、![]() 為非有效態.而將

為非有效態.而將![]() 信號置為有效態,在時鐘的下降沿將數據寫入寄存器。WR3狀態保持

信號置為有效態,在時鐘的下降沿將數據寫入寄存器。WR3狀態保持![]() 有效,WR信號變為無效,進入IDLE態,一次寫周期完成。

有效,WR信號變為無效,進入IDLE態,一次寫周期完成。

評論