一種基于FPGA的誘發電位儀系統研究與設計

O 引言

誘發電位是指對神經系統某一特定部位給予特定刺激后在大腦皮層所產生的特定電活動,對于神經系統功能性異常的疾病有獨特的檢測診斷能力,也是大腦認知和腦機接口研究常用的技術手段。誘發電位儀通常包括視覺誘發電位、聽覺誘發電位和體感誘發電位三種檢測功能,其硬件系統核心組成部分包括:刺激信號源、腦電信號放大和數據采集。刺激信號源包括視覺刺激信號(如棋盤格、黑白閃光等)、聽覺刺激信號和神經刺激信號,一般采用分離設計。

腦電信號數據采集一般包括模/數轉換、數據預處理和數據傳輸等部分,而模/數轉換芯片和主控微處理器芯片的選擇主導了整個數據采集系統的性能。在目前的采集系統中,基于單片機的中低端控制芯片功能較弱,逐漸被DSP和ARM或增強型單片機所取代。DSP芯片采用哈佛結構的流水線工作方式,能實現復雜信號處理算法,如文獻采用DSP實現復雜的腦電信號采集系統;而ARM適合做事務處理或者中低端應用,如文獻中通過ARM處理器建立操作系統實現任務調度。盡管采用DSP和ARM芯片可使系統的運算能力和管理事務的能力得到很大增強,但是構成完整的數據采集系統通常還需要外部邏輯控制器件,尤其不能將數據采集和刺激信號源在單片上集成實現。

由于現代電子技術的飛速發展,可編程邏輯芯片FPGA的集成度越來越高,受到很多廠家和研究機構的關注,利用它的可編程性和可擴展,可將絕大部分的功能集成到FPGA芯片中。如文獻采用FPGA實現了腦電信號采集;文獻則將盲分離算法ICA在FPGA上實現,能同時對腦電信號進行采集和獨立分量分解。

本文針對誘發電位儀的硬件系統設計,提出將信號采集控制、處理、傳輸、刺激信號產生等功能集成在一塊FPGA芯片上的設計方案,并結合ADSl258模/數轉換芯片,使得系統具有16通道,每個通道24位采樣精度和400 kHz采樣率的高性能,而且電路結構簡單。

1 系統總體設計

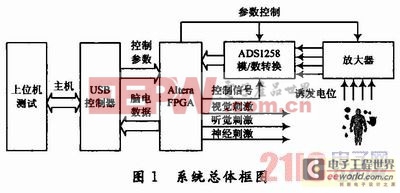

本文提出的誘發電位儀包括了刺激信號源、數據采集和數據傳輸三大部分。其中核心控制芯片采用Altera公司的FPGA,產生刺激誘發信號源包括聽覺刺激、神經傳導刺激和視覺誘發刺激,以及實現對外圍電路如A/D,USB等模塊的控制并在芯片內部集成濾波算法模塊;數據采集采用高精度多通道的模/數轉換芯片ADSl258將通過放大器放大后的誘發電位信號進行模/數轉換并輸入FPGA內進行前置處理;數據傳輸通

過USB控制器Cypress 68013A將誘發電位數據傳輸至PC上位機,由上位機應用程序實現誘發腦電信號的后期處理、顯示、存儲等功能。系統總體框圖見圖1。

評論